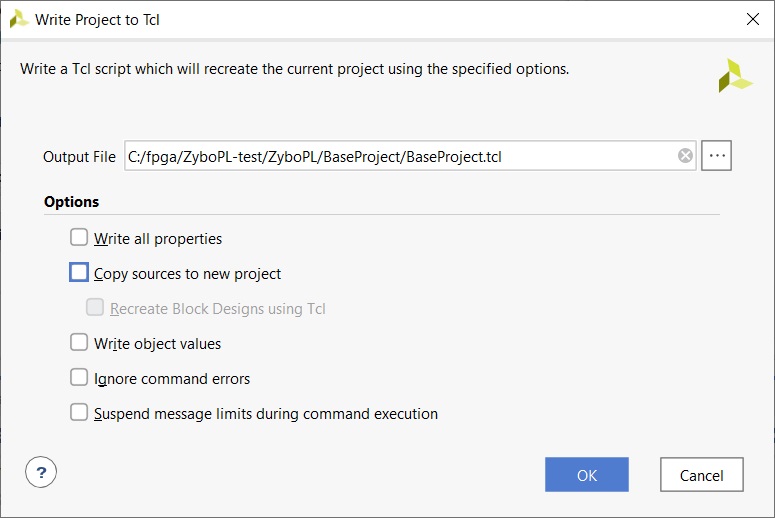

Vivadoのプロジェクトを配布するには VivadoのプロジェクトをGithubに上げる時など、プロジェクトそのまま上げるとファイルが煩雑になるし、XilinxのIPのソースコードをそのまま上げるのも問題がある。 色々 […]

カテゴリー: FPGA/HDL

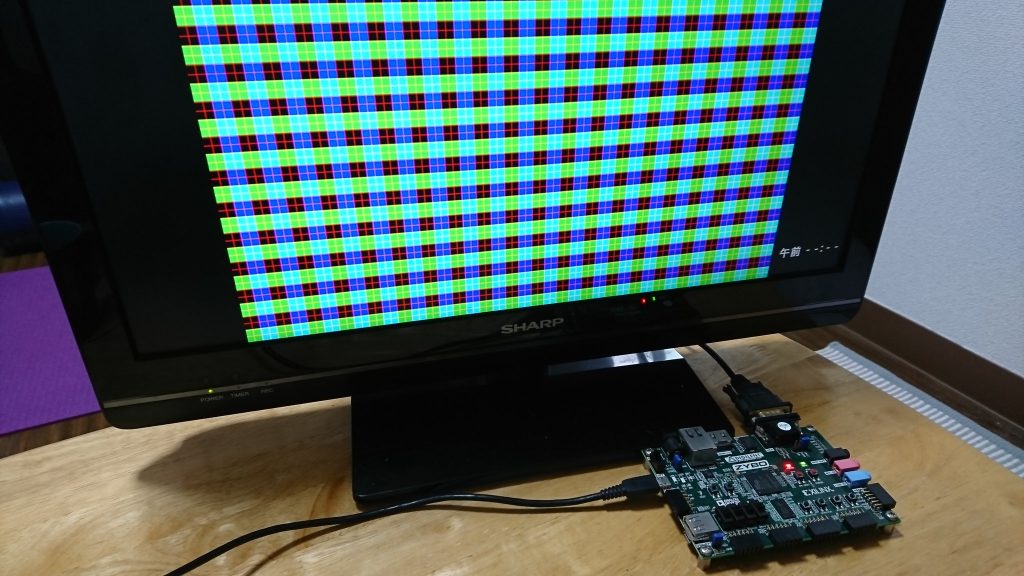

【FPGA】VGAでテストパターンを出力:同期信号とトップモジュール編(FPGA + Verilogでゲーム機をつくろう日記2日目)

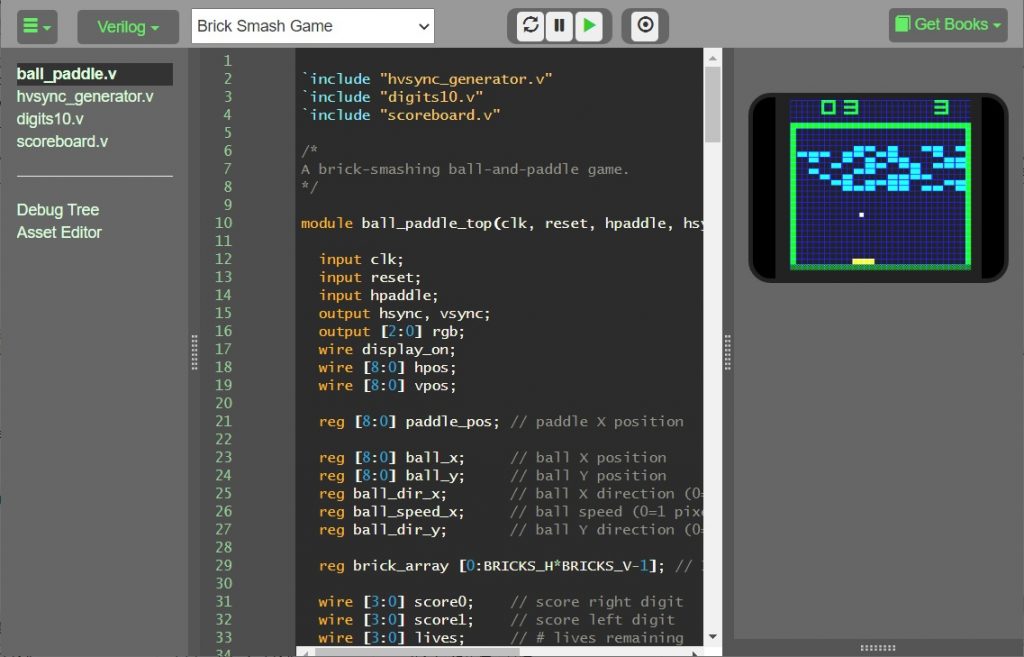

いよいよFPGAに実装 以下の本を読みつつ進めているFPGAでゲーム機をつくろう日記。今回は実際にサンプルコードをFPGAに組み込んで動かしてみる。VGAでの映像出力をやるが、長くなりそうなので2回に分ける。 Desig […]

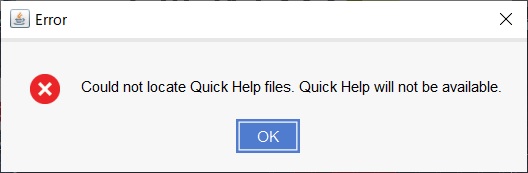

【FPGA/HDL】Windows 10 + Vivado 2020.1で「Could not locate Quick Help files. Quick Help will not be available.」とエラーが出る時の対処法

開発環境 Windows 10 Vivado 2020.1 起動時に必ずエラーが発生 Windows 10にVivado 202.1をインストールして使っているが、起動時に必ず以下の「Could not l […]

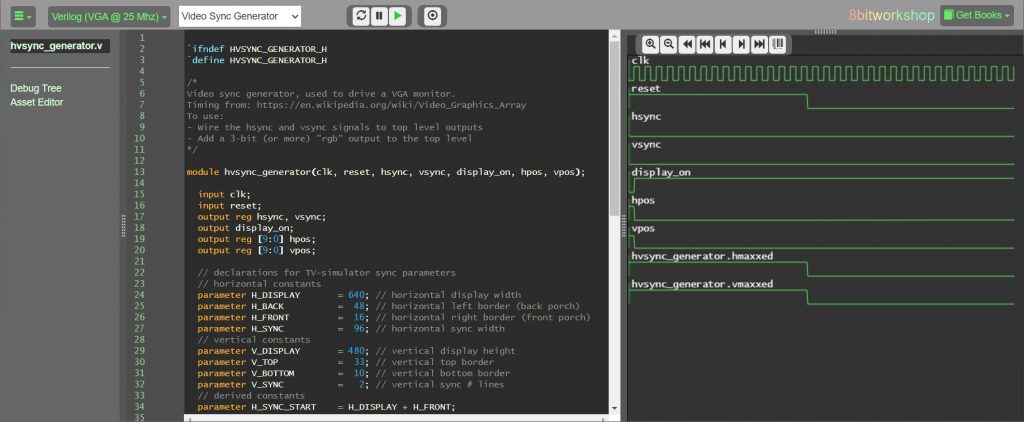

【FPGA】Verilog/HDL解説流し読み&Emulatorでサンプルコードのテスト(FPGA + Verilogでゲーム機をつくろう日記1日目)

まずは本を読み進める 前回紹介した以下の本を読み進めている。序章はverilogのコーディングというより、基礎的な技術や著者製のIDEの紹介がメインになっている。ポイントだけ以下にメモしておく。 Designing Vi […]

【FPGA】FPGA + Verilogでゲーム機をつくろう日記を始めてみる(FPGA + Verilogでゲーム機をつくろう日記0日目)

Verilogでゲーム機をつくる本を買った 最近は仕事でFPGAを触ることが無くなったが、趣味で何かつくることは続けたいと思っている。何かネタ無いかな~と考えて、ゲームと絡めてなんか作れたら面白いかも…と思って「FPGA […]

【FPGA/HDL】Vivado HLS 高位合成体験記6日目:HDLのコードでZYBOのLEDを点滅させる

この日記でやること Vivado HLSの高位合成を使って、ZYBOのLEDを点滅させてみる日記の6日目。前回はDirectiveを指定して、HDLコードを再生成した。今回はこのverilogのコードを、以前作ったZYB […]

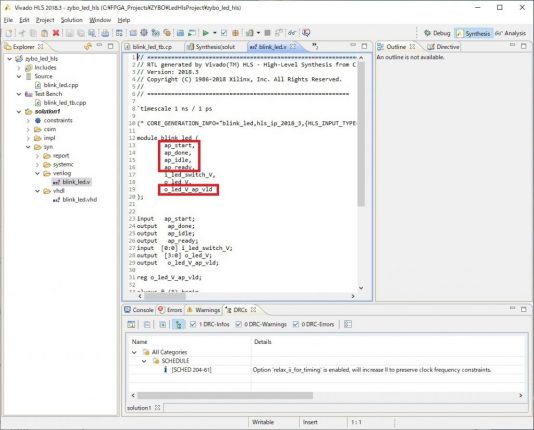

【FPGA/HDL】Vivado HLS 高位合成体験記5日目:Directiveを指定してHDLのコードを最適化する

この日記でやること Vivado HLSの高位合成を使って、ZYBOのLEDを点滅させてみる日記の5日目。前回はC++のコードからHDLのコードを生成してみたが、HDLに不要なポートが付加されていた。今回は、Direct […]

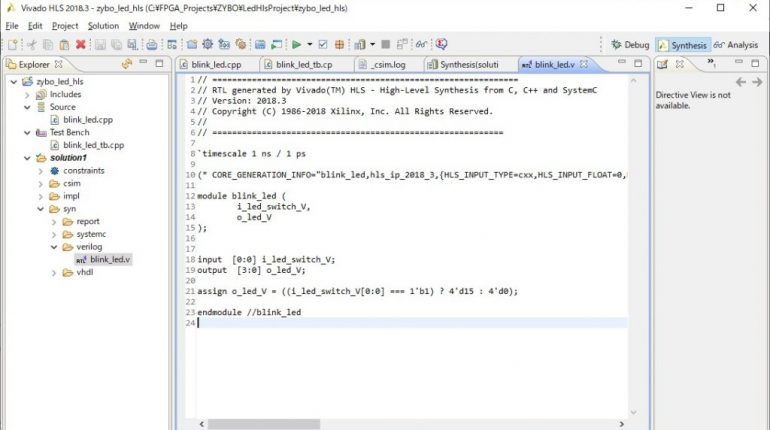

【FPGA/HDL】Vivado HLS 高位合成体験記4日目:C++からHDLのコードを生成

この日記でやること Vivado HLSの高位合成を使って、ZYBOのLEDを点滅させてみる日記の4日目。前回までのところでC++のソースコードを作成&テストベンチで動作の確認を行ったので、今回はいよいよC++のコードか […]

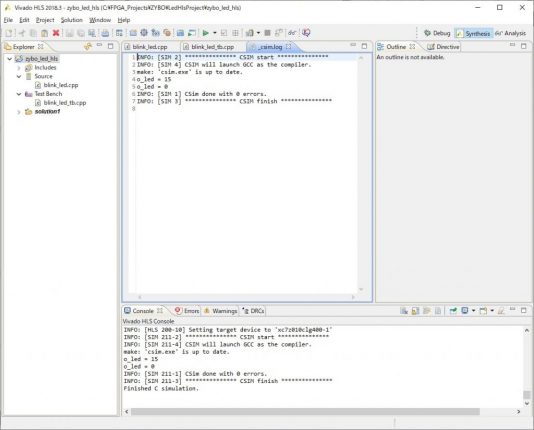

【FPGA/HDL】Vivado HLS 高位合成体験記3日目:C++のテストベンチの作成

この日記でやること Vivado HLSの高位合成を使って、ZYBOのLEDを点滅させてみる日記の3日目。前回はC++のソースコードを作成したので、動作を確認するテストベンチを作成する。 環境 Window […]

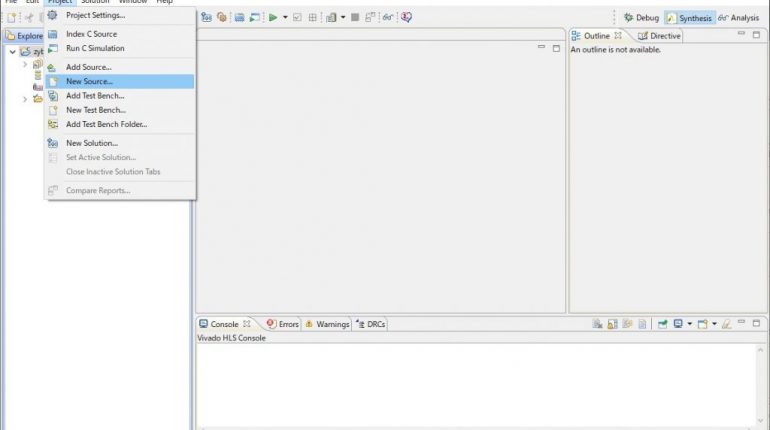

【FPGA/HDL】Vivado HLS 高位合成体験記2日目:C++のソースコードの作成

この日記でやること Vivado HLSの高位合成を使って、ZYBOのLEDを点滅させてみる日記の2日目。前回はプロジェクトの作成をやったので、今回はC++のソースコードを作成していく。 環境 Window […]