この日記でやること

Vivado HLSの高位合成を使って、ZYBOのLEDを点滅させてみる日記の3日目。前回はC++のソースコードを作成したので、動作を確認するテストベンチを作成する。

環境

Windows 10

Vivado HLS 2018.3

ZYBO

C++でテストベンチを作成

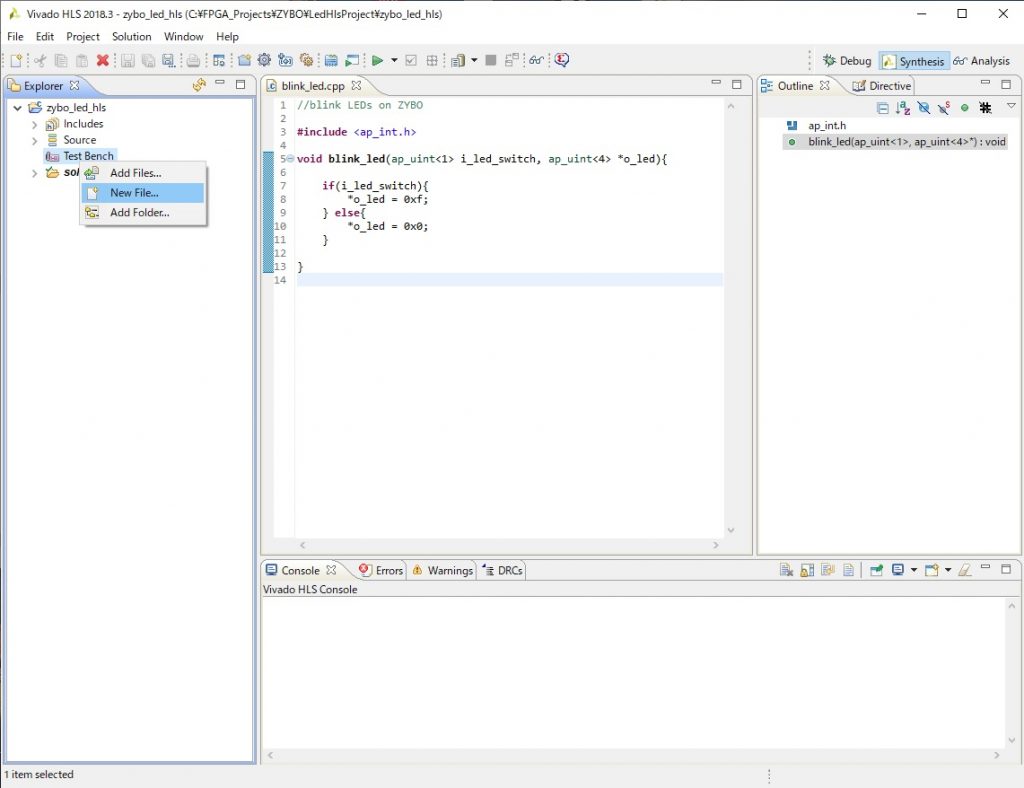

前回はC言語でソースコードをコーディングしたので、今回はTest Benchを作ってソースコードの動作を確認したいと思う。このあたりの流れはverilogで書いているときとあまり変わらない。まず、ExplorerのTest Benchを右クリックして、New File…を選択。

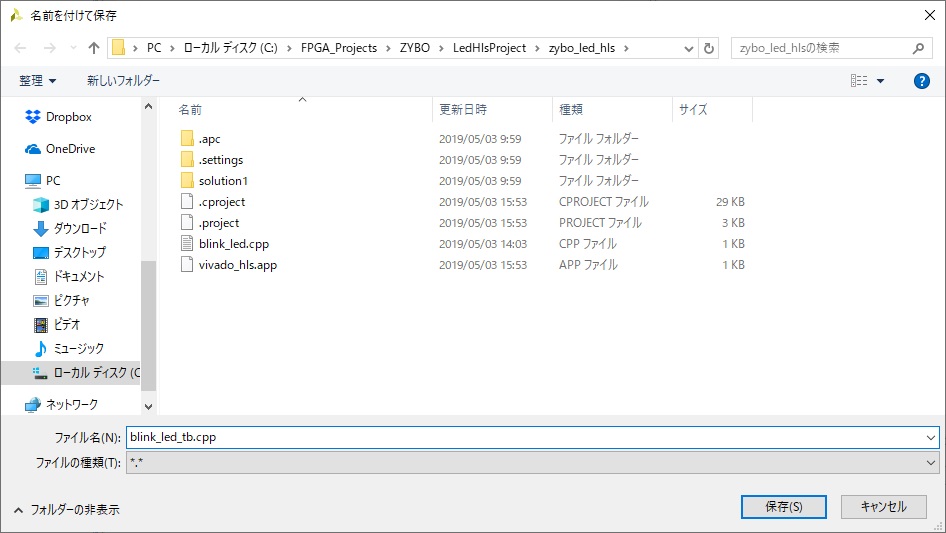

ファイル名は適当にblink_led_tb.cppとして、OKを押す。

するとblink_led_tb.cppが作成され、Vivado HLS上でファイルが開かれる。とりあえずi_led_switchが1の時と0の時の両方の結果が確認できるように、以下のようなテストコードを書いた。

i_led_switchが0のときと1のときに、o_ledの値がそれぞれどうなるかを出力して、結果を確認するテストベンチになっている。このコードでテストを行う。

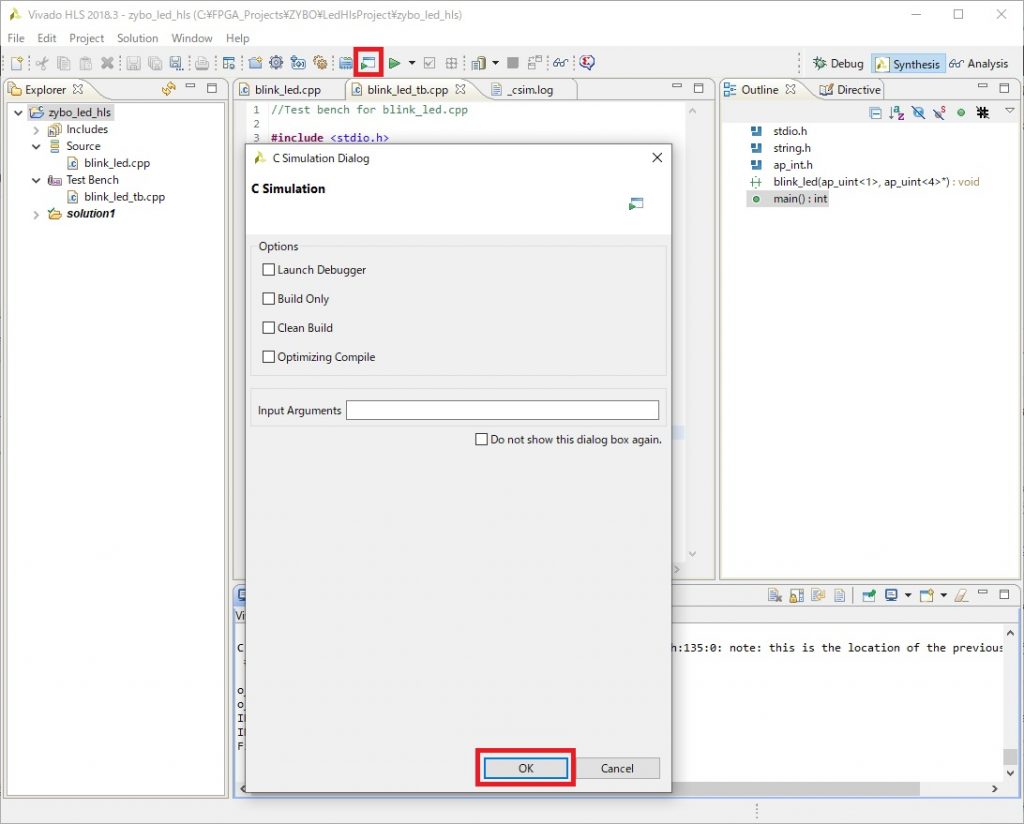

テストベンチを実行

Run C Simulationを選択すると、以下のような画面が出てくるのでそのままOKをクリック。

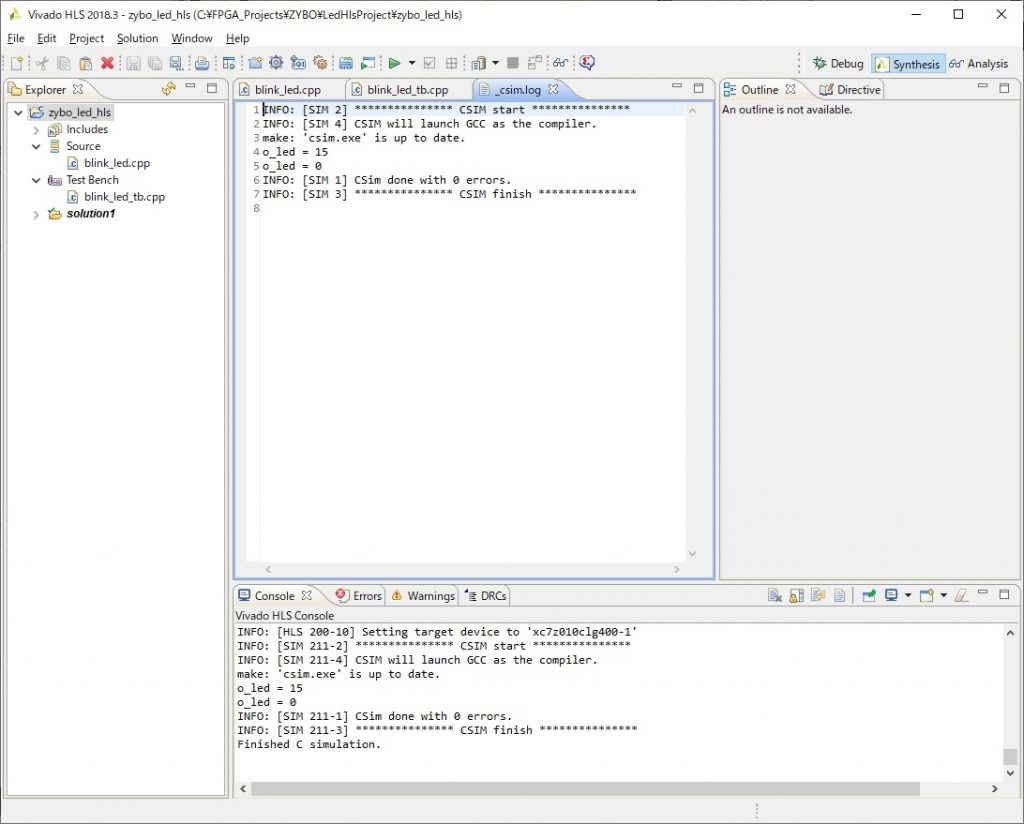

バグが無ければ、以下のようにシミュレーション結果が表示される。狙い通り、i_led_switch=1のときはo_ledが15(16進数だとF)、i_led_switch=0のときはo_ledが0になっている。

C++のソースコードの動きを確認できたので、次はC++のソースコードからVerilog HDLを生成する。

参考文献

公式のドキュメントが以下にあるので、参照しながら進めていきます。

UG871:Vivado Design Suite Tutorial – Hi-Level Synthesis

UG902:Vivado Design Suite User Guide – Hi-Level Synthesis

以下の資料も参考にさせて頂きました。

https://www.slideshare.net/marsee101/vivado-hls1

ZYBOで遊ぼう日記まとめ

ZYBO関係の記事は、大まかな内容ごとに以下にまとめています。

https://wakky.tech/zybo/