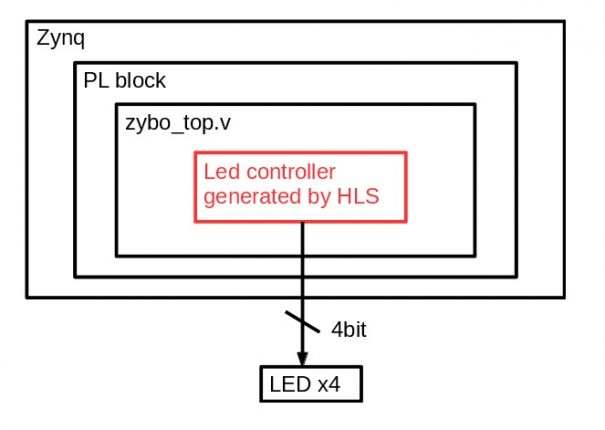

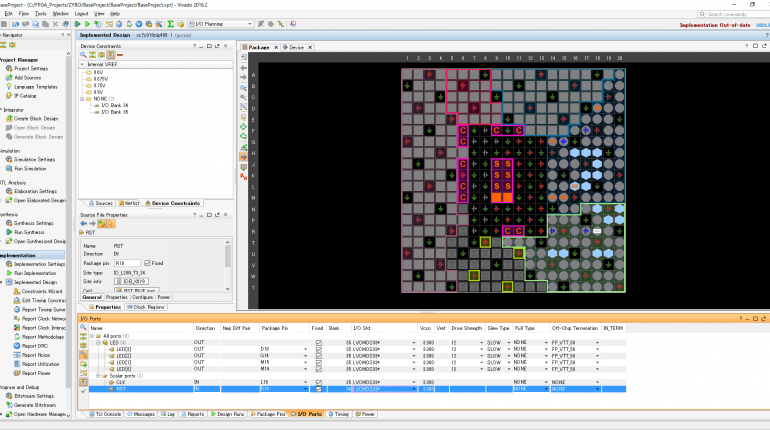

この日記でやること Vivado HLSの高位合成を使って、ZYBOのLEDを点滅させてみる日記の6日目。前回はDirectiveを指定して、HDLコードを再生成した。今回はこのverilogのコードを、以前作ったZYB […]

タグ: FPGA

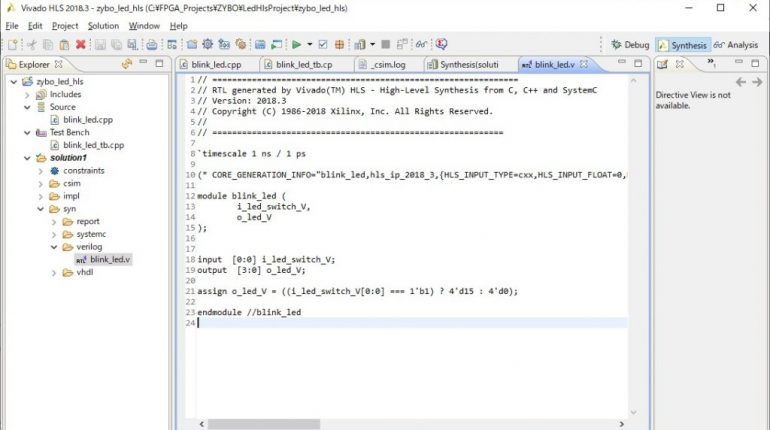

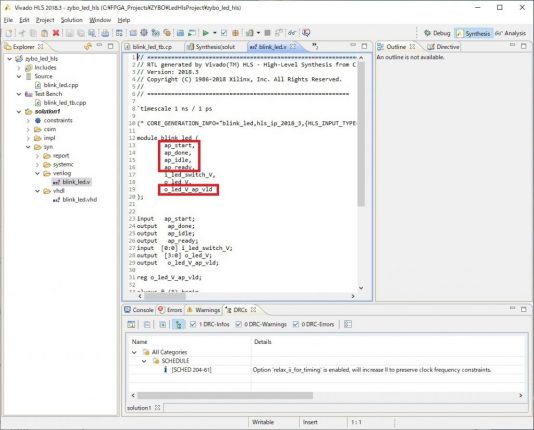

【FPGA/HDL】Vivado HLS 高位合成体験記5日目:Directiveを指定してHDLのコードを最適化する

この日記でやること Vivado HLSの高位合成を使って、ZYBOのLEDを点滅させてみる日記の5日目。前回はC++のコードからHDLのコードを生成してみたが、HDLに不要なポートが付加されていた。今回は、Direct […]

【FPGA/HDL】Vivado HLS 高位合成体験記4日目:C++からHDLのコードを生成

この日記でやること Vivado HLSの高位合成を使って、ZYBOのLEDを点滅させてみる日記の4日目。前回までのところでC++のソースコードを作成&テストベンチで動作の確認を行ったので、今回はいよいよC++のコードか […]

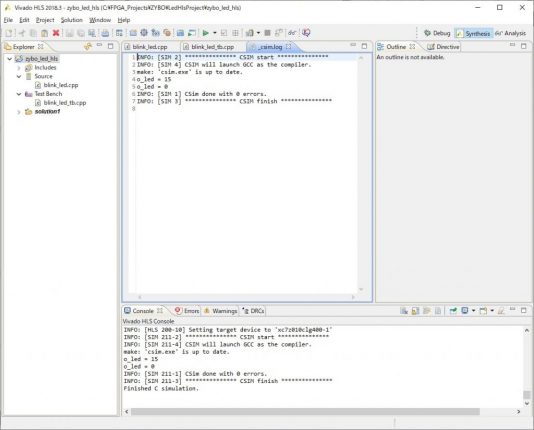

【FPGA/HDL】Vivado HLS 高位合成体験記3日目:C++のテストベンチの作成

この日記でやること Vivado HLSの高位合成を使って、ZYBOのLEDを点滅させてみる日記の3日目。前回はC++のソースコードを作成したので、動作を確認するテストベンチを作成する。 環境 Window […]

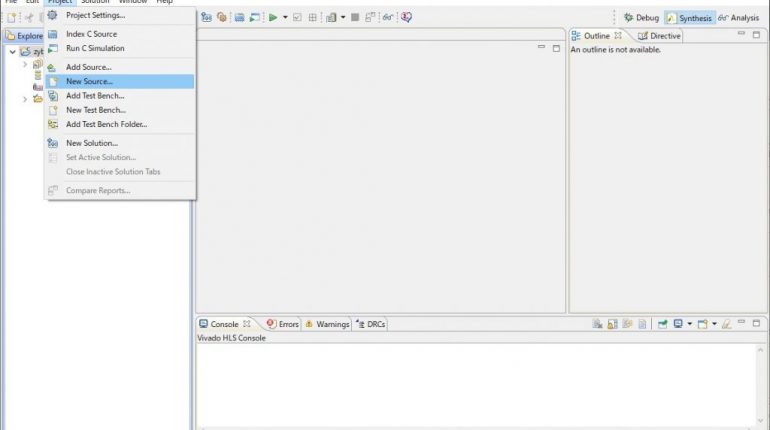

【FPGA/HDL】Vivado HLS 高位合成体験記2日目:C++のソースコードの作成

この日記でやること Vivado HLSの高位合成を使って、ZYBOのLEDを点滅させてみる日記の2日目。前回はプロジェクトの作成をやったので、今回はC++のソースコードを作成していく。 環境 Window […]

【FPGA/HDL】Vivado HLS 高位合成体験記1日目:プロジェクトの作成

この日記でやること 今まで高位合成(※)に触れようと思いつつ、なかなか機会が無かった。そこで今回は、Xilinx社のVivado HLSというツールで高位合成にチャレンジしてみようと思う。以前は有料ライセンスが必要だった […]

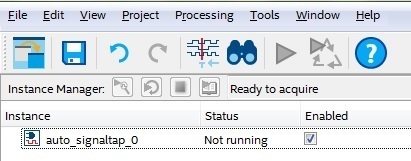

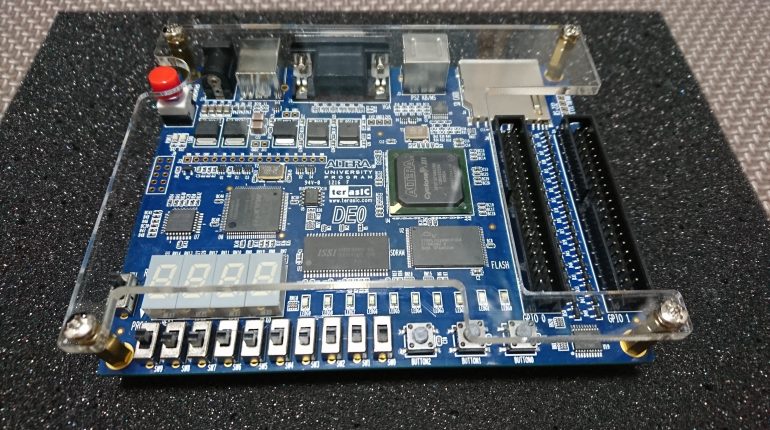

【FPGA/HDL】SignalTap II Logic Analyzerで「Ready to acquire」と表示されているのに実行(Run Analysis)が押せない

タイトルの通り、SignalTap II Logic Analyzerで「Ready to acquire」と表示されているのにも関わらず、実行(Run Analysis)が押せないことがあった。原因はしょーもないことだ […]

【FPGA/HDL】Nios II SBT for Eclipseで「symbol std could not resolved」errorと出るときの対処

最近、Nios IIを使う機会があるが、Nios II 16.1 Software Build Tools for EclipseでBuildしようとすると「symbol std could not resolved」と […]

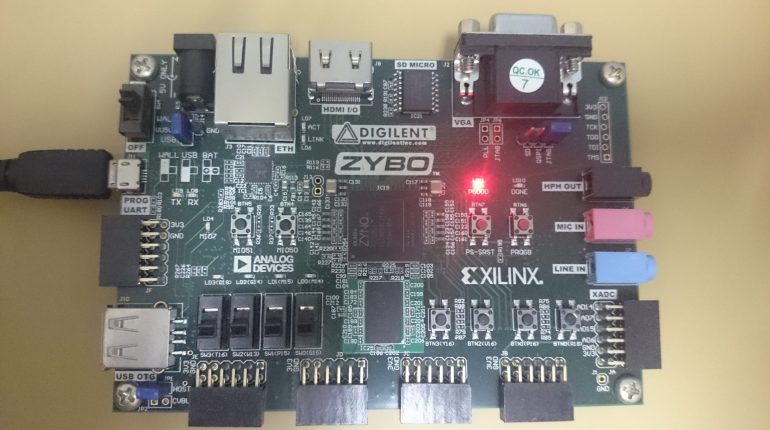

【FPGA/HDL】FPGAのPLブロックだけを使ってLチカ日記 3日目:ZYBOにJTAG経由でbitファイル書き込んでLED点滅)

今回やること 前回、ZYBOのLEDファイルを点滅させるRTLを書き、bitファイルを作成した。今回はいよいよZYBOにbitファイルを書き込み、LEDを点滅させてみたいと思う。いわゆるLチカ。 環境 Wi […]

【FPGA/HDL】FPGAのPLブロックだけを使ってLチカ日記 2日目:Vivado 2016.2 でZYBOのトップモジュール(LED点滅)を作成

今回やること 前回、ZYBO用のプロジェクトの作成まで行った。今回は、トップモジュールのRTLを書いてみる。 ZYBOの入門ではARMを含むPSブロックを使って、「Hello World」からやるパターンが多いみたい。そ […]