この日記でやること

Vivado HLSの高位合成を使って、ZYBOのLEDを点滅させてみる日記の6日目。前回はDirectiveを指定して、HDLコードを再生成した。今回はこのverilogのコードを、以前作ったZYBOのRTLに組み込んで、LEDを点滅させてみたいと思う。

環境

Windows 10

Vivado HLS 2018.3

Vivado 2018.3

ZYBO

ZYBO用のプロジェクトを作成

また1からプロジェクトを作り始めるのは大変なので、以前「FPGAのPLブロックだけを使ってLチカ日記」で作成したprojectをフォルダごとコピーして使う。コピーしたフォルダにはHlsProjectという名前をつけた。ちょっとわかりにくいが、HlsProjectというフォルダの以下にBaseProjectというフォルダがあり、この中にVivadoのプロジェクトファイルなどが入っている。verilogのコードはrtlというフォルダの中にまとめている。このrtlフォルダの中に、Vivado HLSでC++のコードから生成したverilogのファイルをコピーしておく。

Vivado 2018.3でプロジェクトを開いてverilogファイルを追加する

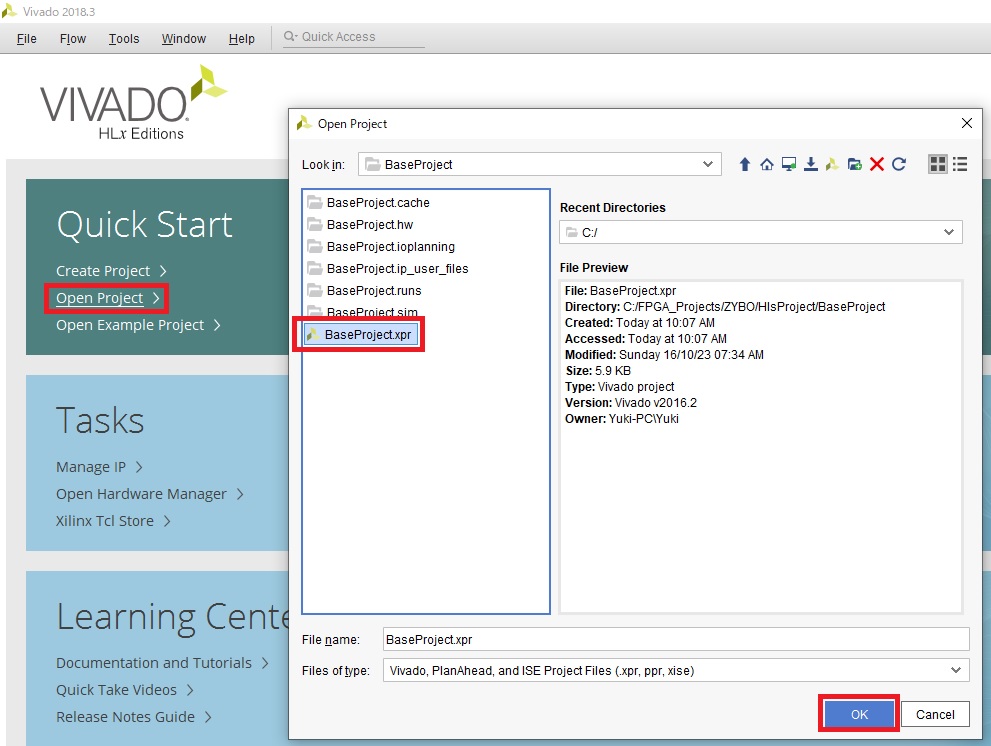

先ほどコピーしたプロジェクトを、Vivado 2018.3(HLSでは無くて普通のVivado)で開く。

開いたら、FileからAdd Sourcesを選択して、先ほどコピーしたverilogファイルblink_led.vをプロジェクトに追加する。

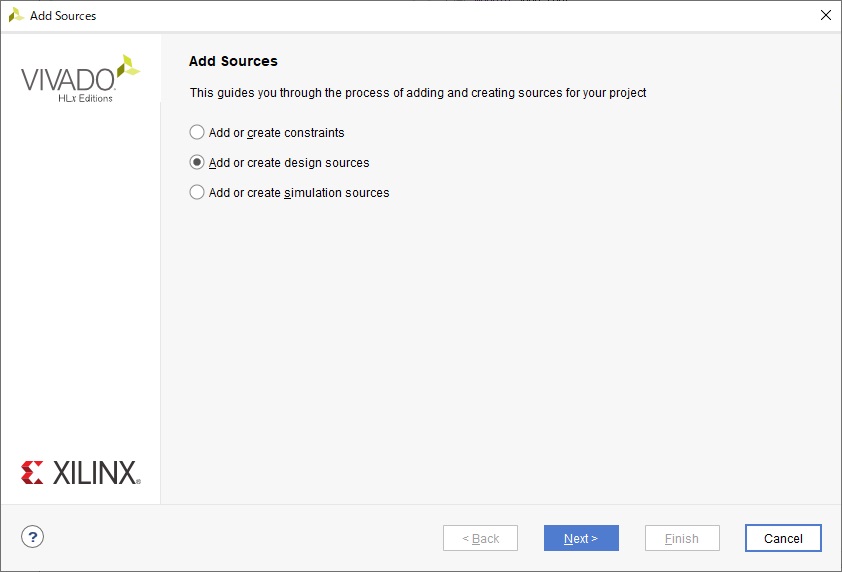

以下の画面が出てくるので、Add or create design sourcesを選択する。

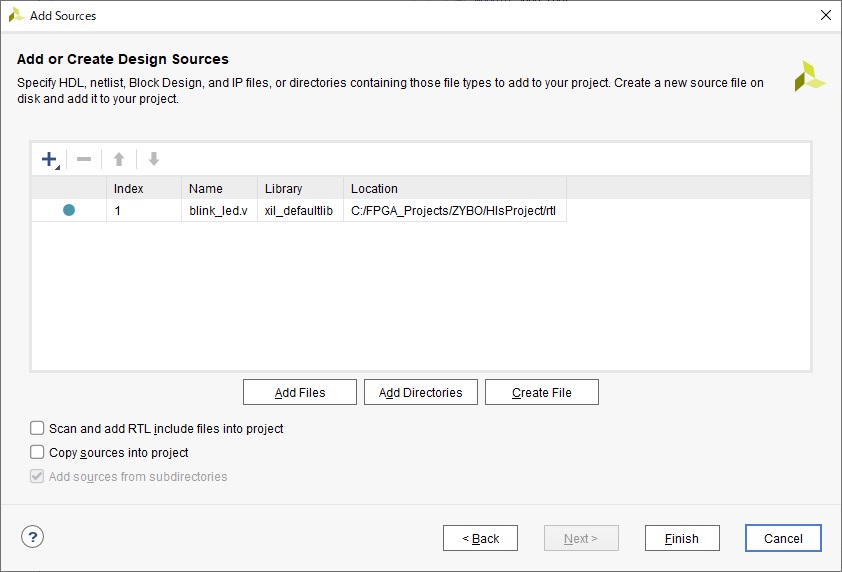

Add Filesからblink_led.vを選択して、Finishをクリック。

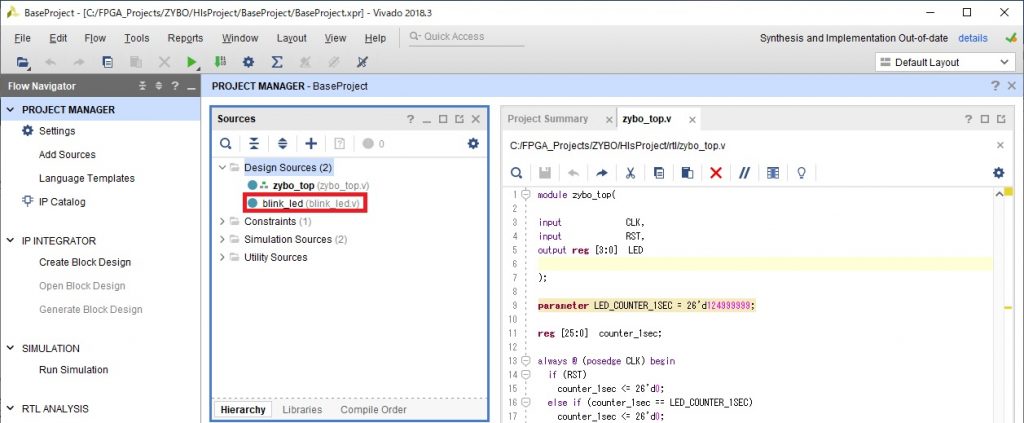

これでファイルの追加が完了。Vivado上でも、Deseign Sourcesにblink_led.vが追加されたことが確認できる。

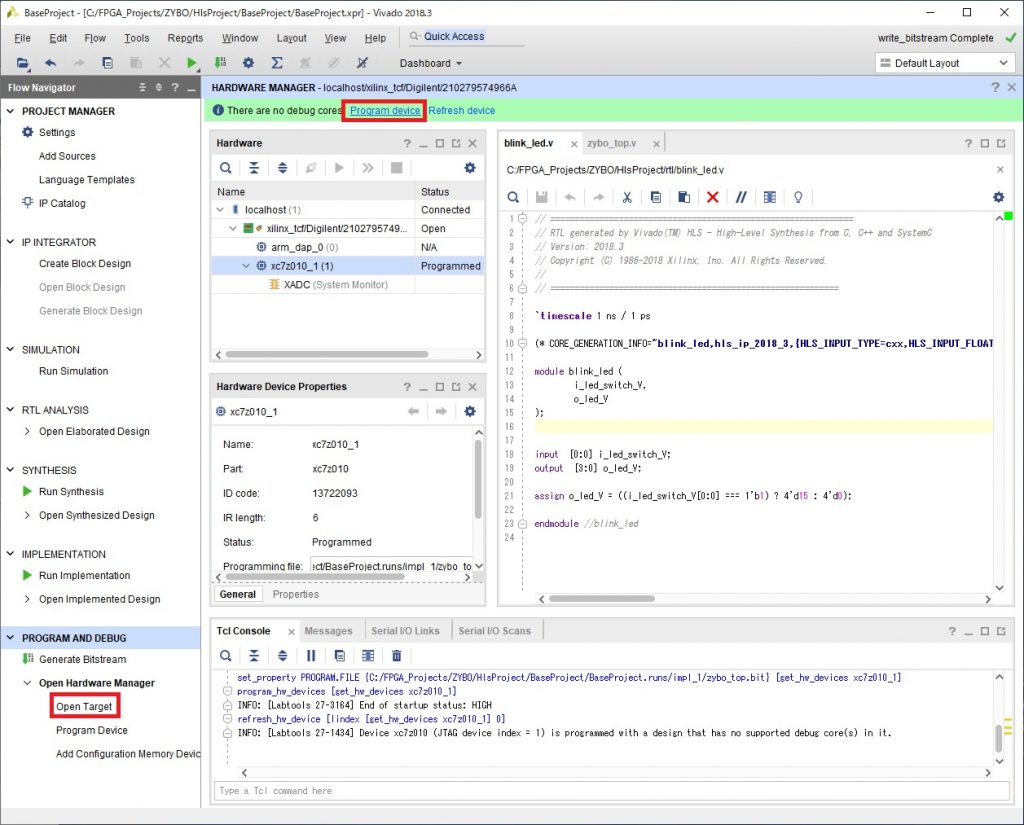

高位合成したverilogファイルのImplementとZYBOへの書き込み

以前作成したzybo_top.vを以下のように書き換えて、blink_ledを組み込む。

約1秒ごとにalways文でLEDを点滅させていたのを、およそ0.5秒ごとにblink_ledを使ってLED全点灯と全消灯を繰り返すように変更した。あとはこれをいつも通りコンパイルして、ZYBOに書き込む。Geneate Bitstreamを実行すれば、Synthesis、Implementation、Bitstreamの生成まで一気にできる。

あとはZYBOにUSBをつなぎ、Program Deviceを実行すれば完了。

以下が実際に光っている様子。ちゃんとLEDが全点灯と全消灯を繰り返している。

Vivado HLSでC++から高位合成したHDLコードを組み込んで、ZYBOをLチカ。日記も書き溜めできたし、GW中のFPGAの勉強はこのくらいにしておくか。 pic.twitter.com/32pNcotXh1

— Wakky (@wakky_free) 2019年5月4日

今回は高位合成してできたverilogコードをそのままコピーしてきて組み込んだけど、ブロックデザインで使う場合にはIPとしてパッキングする必要があると思う。余力があったら、そのあたりも引き続き書いていきたい。

参考文献

公式のドキュメントが以下にあるので、参照しながら進めていきます。

UG871:Vivado Design Suite Tutorial – Hi-Level Synthesis

UG902:Vivado Design Suite User Guide – Hi-Level Synthesis

以下の資料も参考にさせて頂きました。

https://www.slideshare.net/marsee101/vivado-hls1

ZYBOで遊ぼう日記まとめ

ZYBO関係の記事は、大まかな内容ごとに以下にまとめています。

https://wakky.tech/zybo/