この日記でやること

Vivado HLSの高位合成を使って、ZYBOのLEDを点滅させてみる日記の4日目。前回までのところでC++のソースコードを作成&テストベンチで動作の確認を行ったので、今回はいよいよC++のコードからHDLのコードを生成してみる。

環境

Windows 10

Vivado HLS 2018.3

ZYBO

Top Functionを指定する

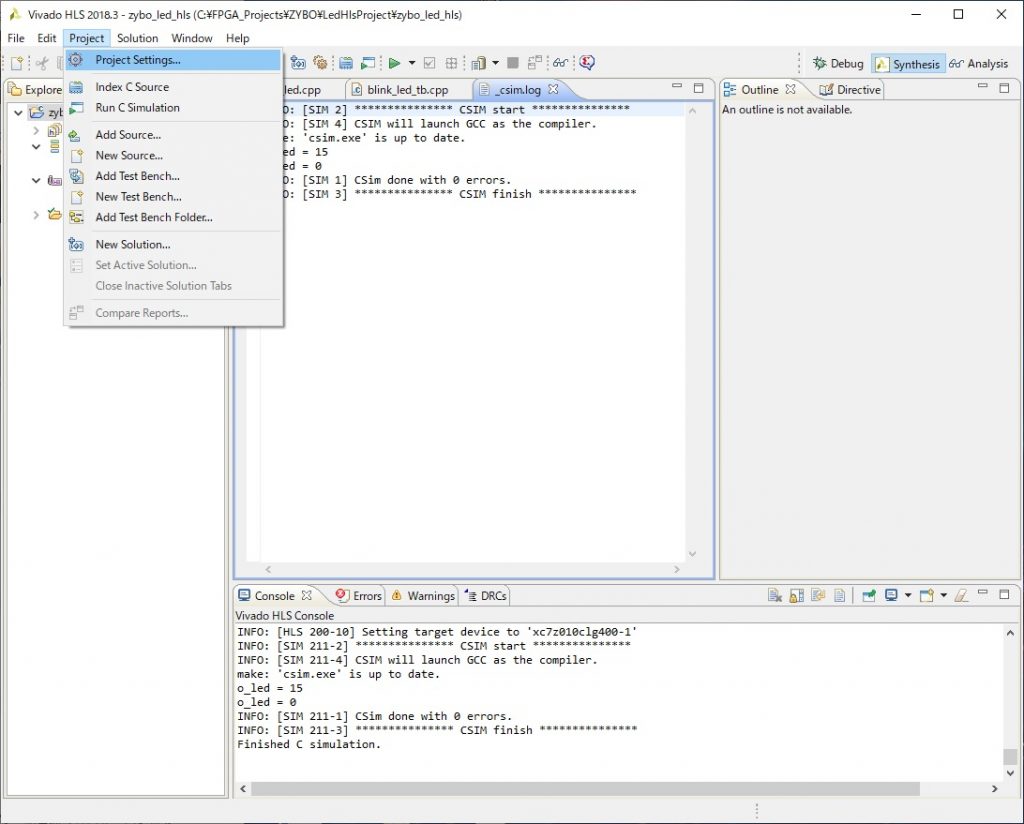

Projectを作成した時はCのソースコードをつくっておらず、Top Functionを指定しなかったので、改めてTop Functionを指定する。ProjectからProject Settings…を選択する。

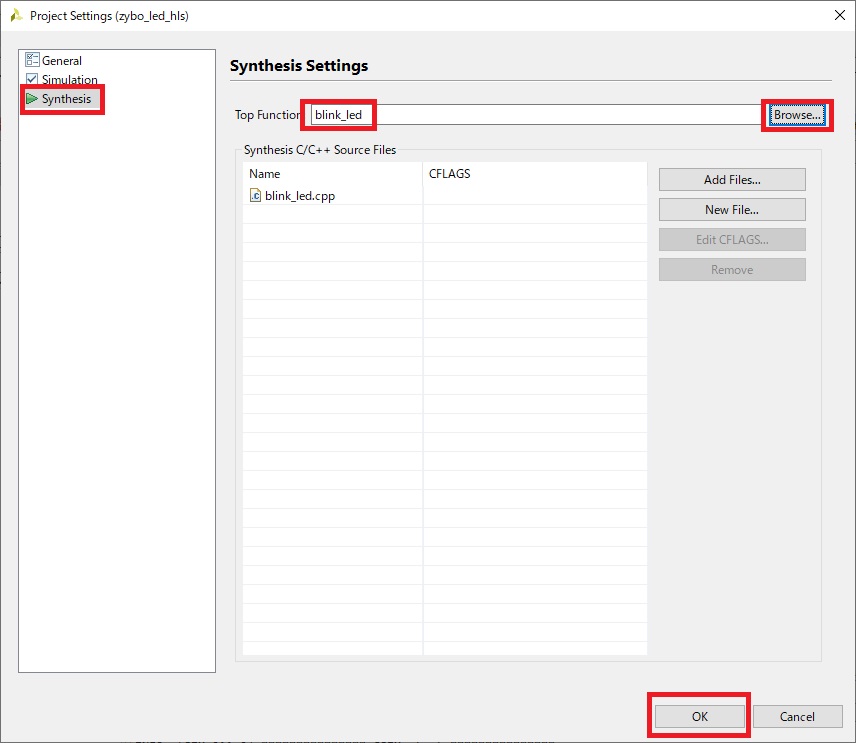

Synthesisを選び、Top Functionでblink_led.cppを選択して、OKをクリックする。

C言語のソースコードを合成してHDLコードを生成する

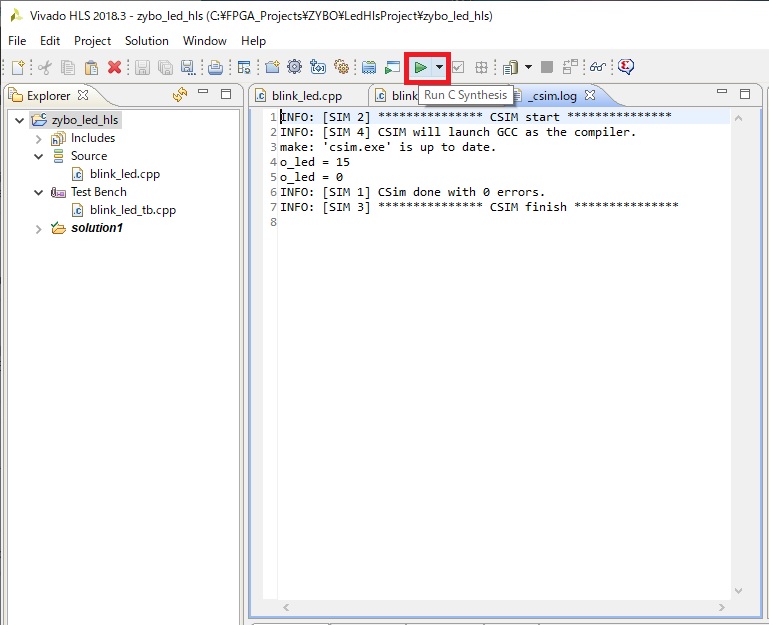

Vivado HLSに戻り、Run C Synthesisを押すとCの合成が開始される。

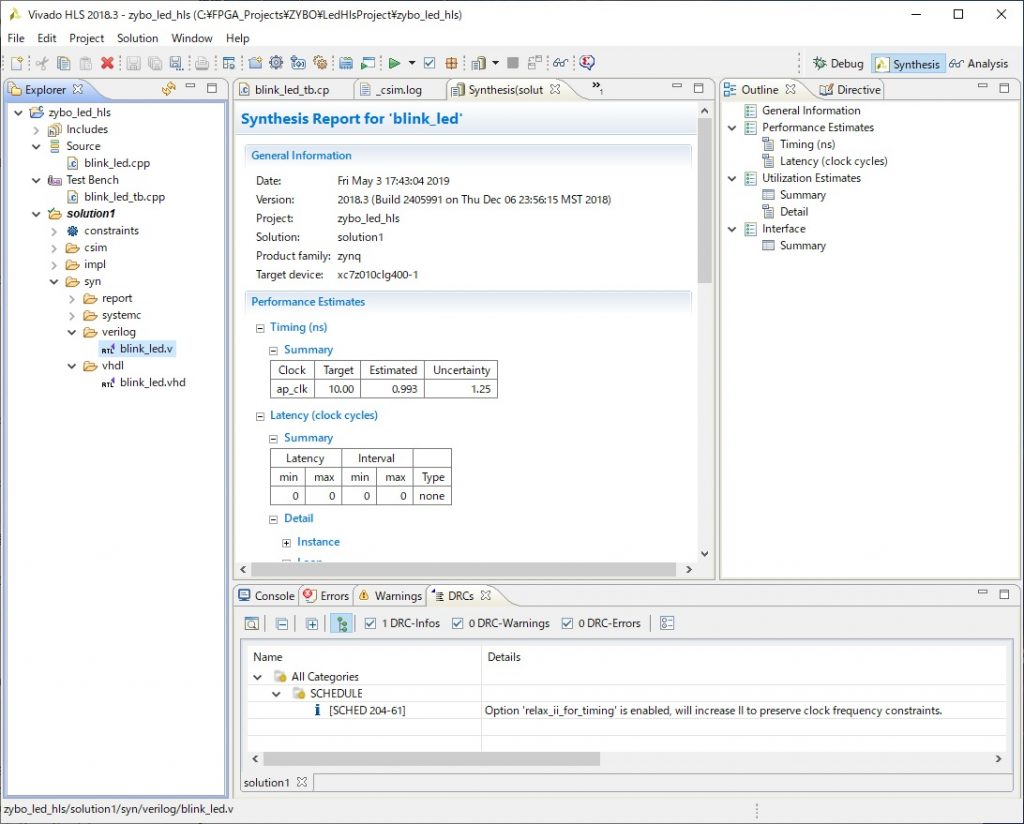

バグが無ければ、以下のように合成結果が表示される。

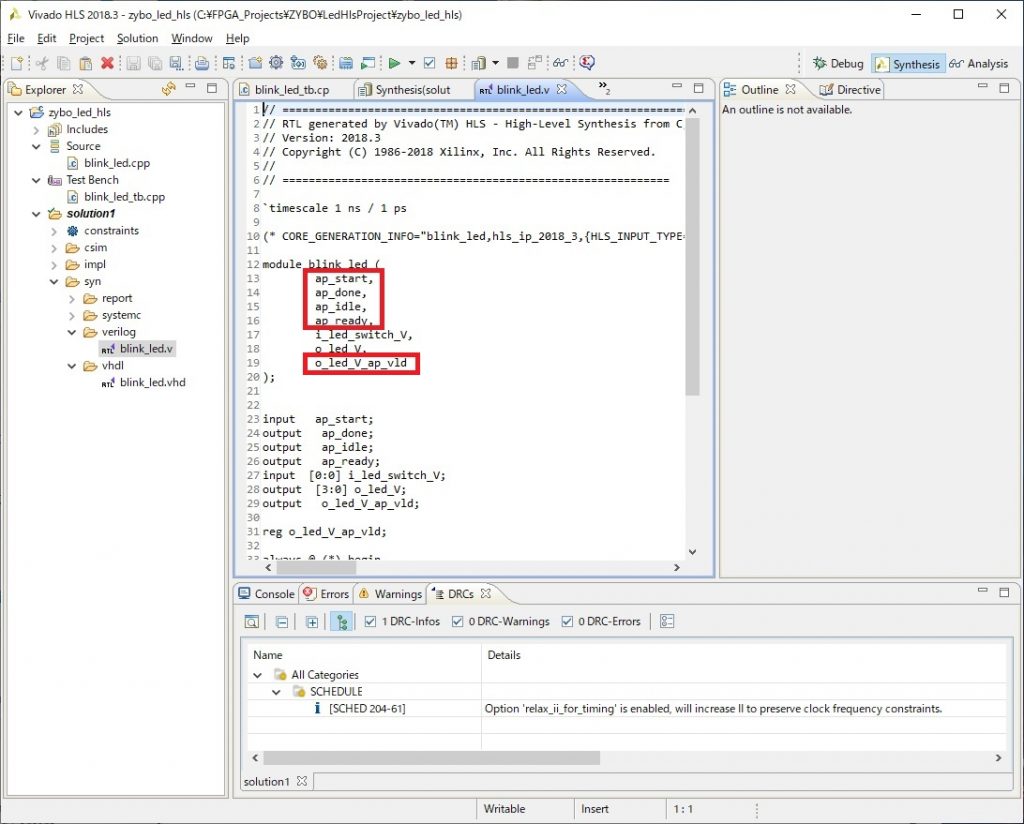

詳しいレポートの見方はまたおいおい勉強するとして、生成されたverilogファイルの中身を確認する。synフォルダ以下のverilog、vhdlのフォルダに、verilogとvhdlそれぞれで生成されたHDLファイルが生成されている。私はverilogを使っているので、blink_led.vを試しに開いてみる。c言語で記述したポートのほかに、ap_start、ap_done、ap_idle、ap_readyというポートと、o_led_V_ap_vldという見慣れない入出力ポートがある。

こちらはVivado HLSがmoduleの制御のために付加したインタフェースである。このインターフェースに合わせて周辺のRTLを設計してももちろん良いが、今回はシンプルにi_led_switchとo_ledだけの入出力を持つHDLにしたい。ということで、次回はDirective(指示子)をソースコードに追加してHDLを最適化し、Vivado HLSがこちらの意図どおりの合成を行ってくれるようにしたいと思う。

参考文献

公式のドキュメントが以下にあるので、参照しながら進めていきます。

UG871:Vivado Design Suite Tutorial – Hi-Level Synthesis

UG902:Vivado Design Suite User Guide – Hi-Level Synthesis

以下の資料も参考にさせて頂きました。

https://www.slideshare.net/marsee101/vivado-hls1

ZYBOで遊ぼう日記まとめ

ZYBO関係の記事は、大まかな内容ごとに以下にまとめています。

https://wakky.tech/zybo/