Visual Studio Codeがなかなか良いらしい

Visual Studio Code(VSC)を会社の方がVerilogのエディタとしてプッシュしていたので、気になっていた。ネットで調べてみたところ、

- 動作が軽い

- 拡張機能を入れれば細かい設定をしなくても使いやすい

- カスタマイズ性も高い

など、評判が良い。今のところSublime TextにVerilogのpackageを入れて使っているが、色々と試して良いものを取り入れていきたい。というわけで、今回はVSCを導入して、VerilogのExtention(拡張機能プラグイン)を入れてみる。

環境

Windows 10

Visual Studio Codeのダウンロード

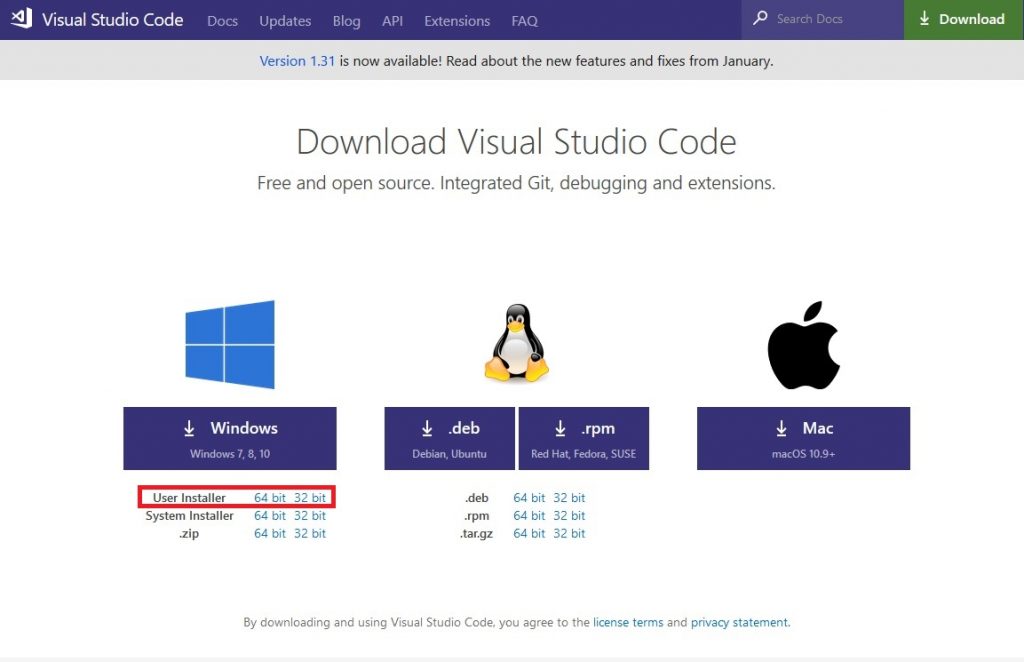

以下のサイトから無料でダウンロードできる。特にわずらわしい登録もいらない。

https://code.visualstudio.com/download

ここから自分のOSに合ったインストール用のファイルをダウンロードする。私はWindows10 64bitのPCを使っているで、Windows10 64bit のUser Installerでインストールを行った(User InstallerとSystem Installerの違いはこちら)。

Visual Studio Codeのインストール

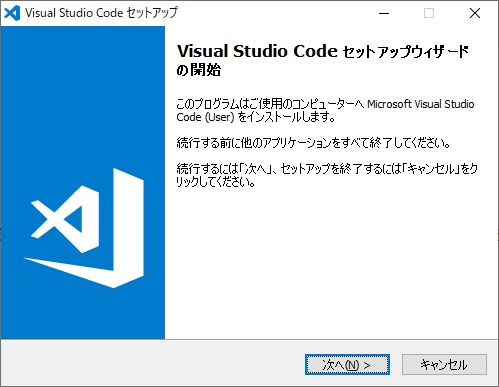

ダウンロードしたインストーラーをダブルクリックして立ち上げると、セットアップウィザードが立ち上がるので「次へ」をクリック。

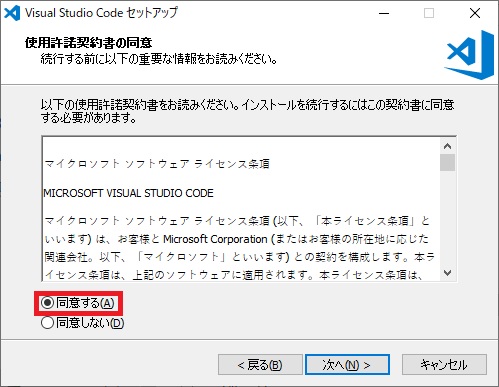

すると使用許諾契約書の画面になるので、ざっと読んで「同意する」を選択して「次へ」をクリック。

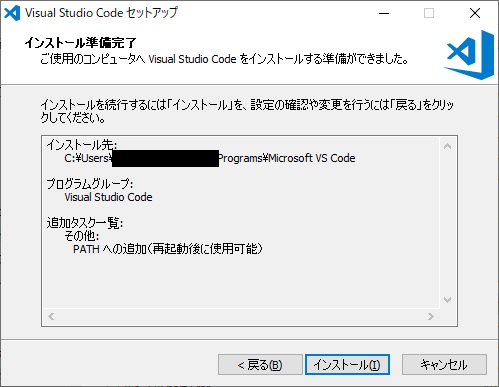

インストール先など特に変える必要が無ければ、デフォルトのまま「次へ」をクリックして行けばOK。最後に以下の画面になるので、「インストール」をクリックする。

インストールが終了すると以下の画面になる。これでインストールは完了。今回はこのままVerilogのExtentionを入れようと思うので、「Visual Studio Codeを実行する」にチェックを入れたまま「完了」をクリック。

VerilogのExtentionを追加

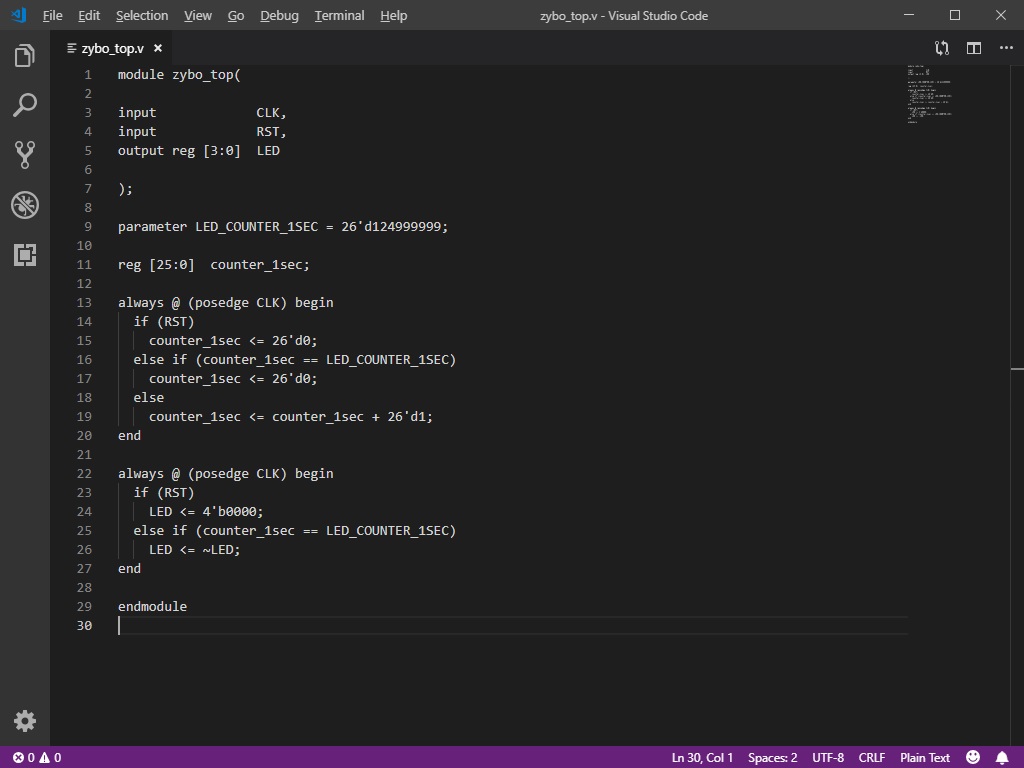

初期の状態で、試しにverilogのソースコードを開いてみる。デフォルトではシンタックスハイライト(色分け)などもなく、以下のような状態になっている。

この状態だとかなり使いづらいので、verilogに対応したExtentionを入れてみる。まず、左側の一番下のアイコンをクリックし、検索欄に「verilog」と入れる。一番上に出てきた「Verilog HDL/System Verilog」が使いやすいと評判なので、今回はこちらを使ってみる。Extentionをクリックし、Installを押せばOK。

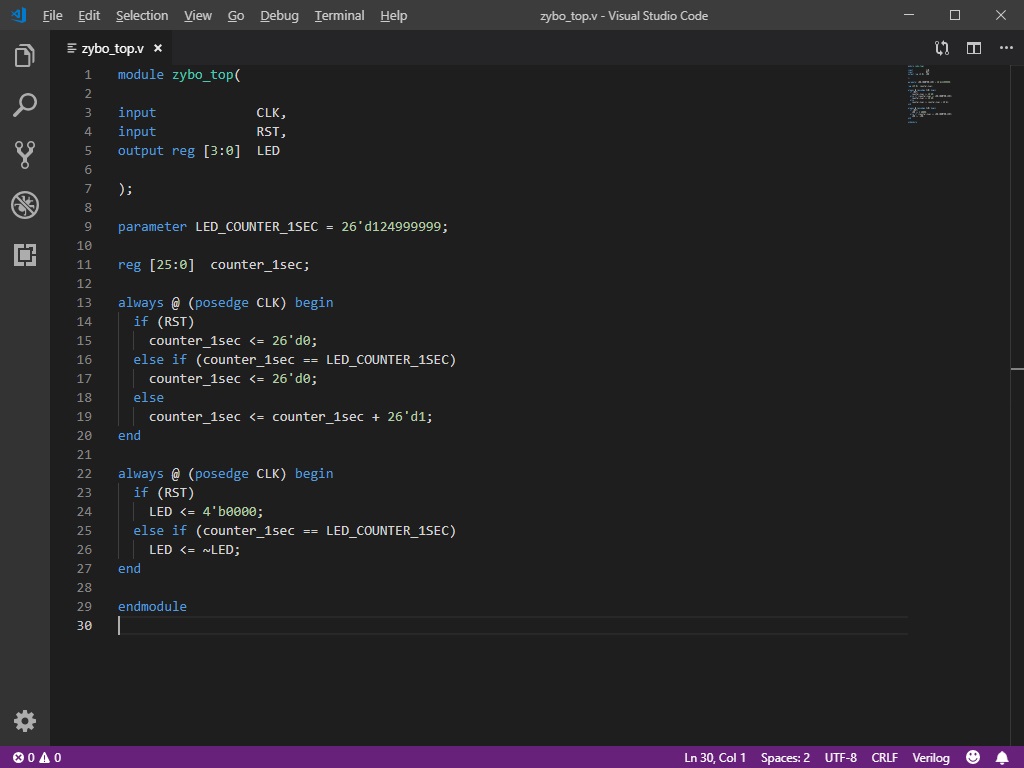

この状態でverilogのソースコードを見てみると、シンタックスハイライトされて見やすくなっている。また、moduleやalwaysなど、よく使う定型文をスニペットとして呼び出せるようになっいて非常に便利。

modelsimなどのsimulatorとの提携も出来るようだし、VSCの機能として、簡単に自分でスニペットを定義することもできる。これから色々カスタマイズしてみたいと思うが、とりあえず今回はここまで。