Vivadoのプロジェクトを配布するには

VivadoのプロジェクトをGithubに上げる時など、プロジェクトそのまま上げるとファイルが煩雑になるし、XilinxのIPのソースコードをそのまま上げるのも問題がある。

色々な人がGithubにアップロードしているレポジトリを見るとtclファイルにして書き出したものをアップロードしている人が多いようだ。tclファイルからVivadoのプロジェクトを作成することができるし、tclファイルは非常に容量が小さいファイルなので、この方法が一番スマートに思える。

ということで、今回はまずVivadoのプロジェクトをtclファイルに書き出す方法をメモしておく。

環境

Windows 10

Vivado 2020.1

Vivado 2020.1でtclファイルを書きだす

まず以前やったLチカのプロジェクトをtclで書き出してみる。

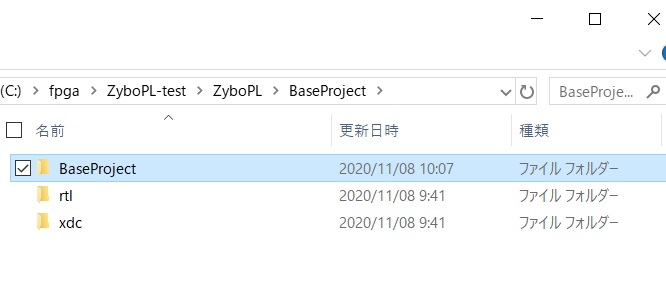

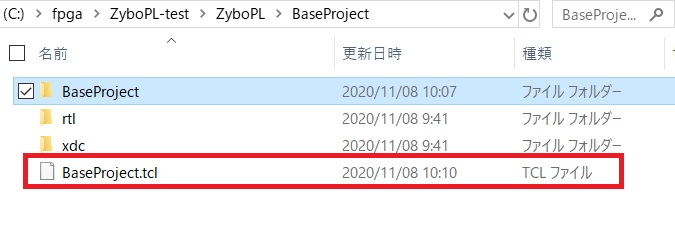

私のプロジェクトのディレクトリ構成は以下のようになっていて、rtlの中にverilodのコード、xdcの中に制約ファイル、そしてBaseProjectというディレクトリの中にVivadoのプロジェクトファイル(.xpr)やその他Vivadoで生成されたファイルが入っている。

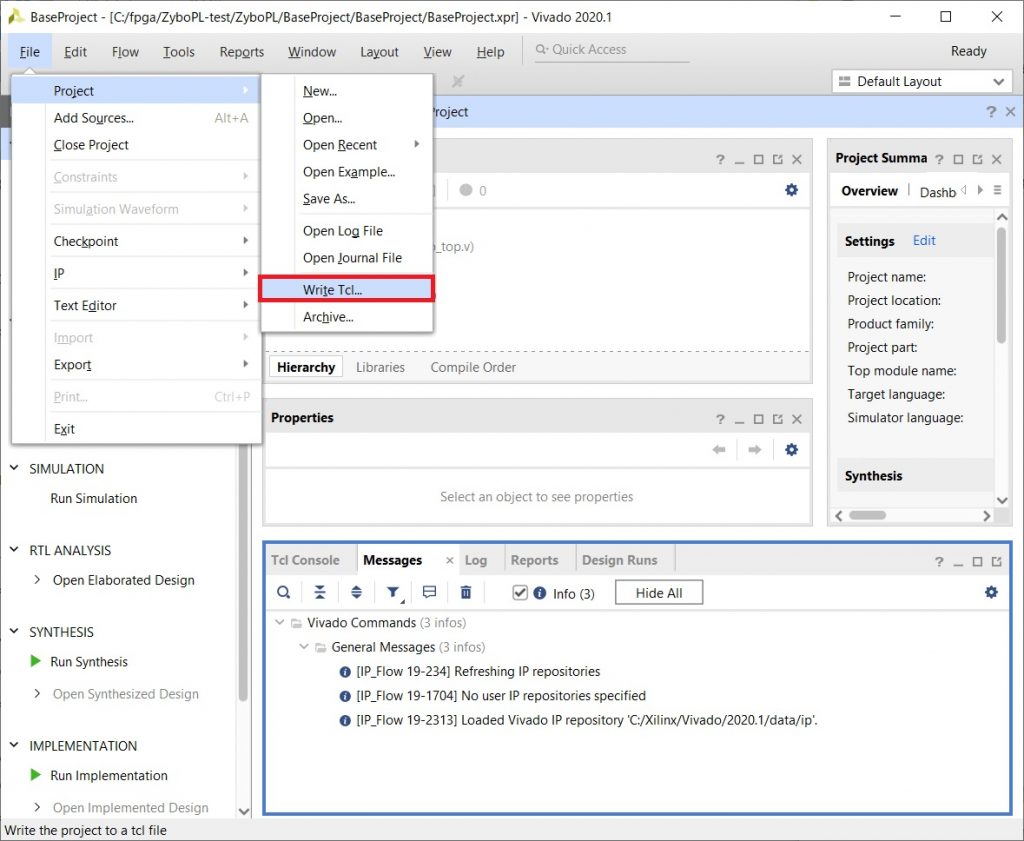

まずは、tclファイルとして書き出したいプロジェクトを開く。今回の私の場合はBaseProjectディレクトリの中のBaseProject.xprというプロジェクトを開く。そして、ツールバーからFile → Project → Write Tclを選択する。

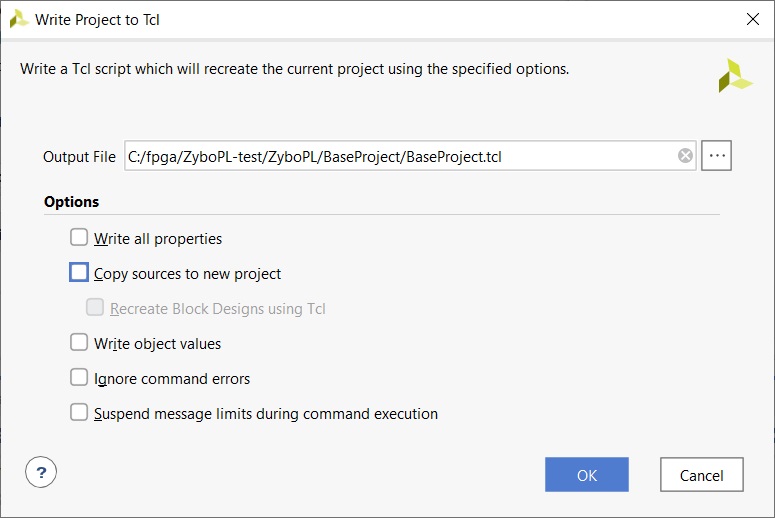

すると以下のようなダイアログが出るので、tclの出力先を選んだうえで「Copy sources to new project」のチェックは外してOKをクリックするとtclの生成がスタートする。今回はrtlやxdcと同じ階層にtclを出力するようにした。

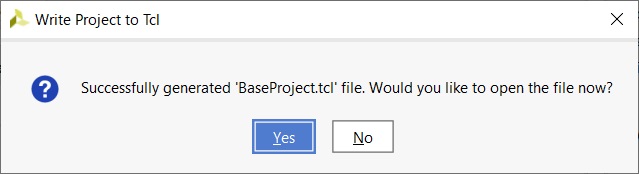

問題なく終了すれば以下のようなダイアログが出る。配布用であれば開く必要は無いのでNoを選んで終了。

すると、以下のように選択したディレクトリに.tclファイルが生成されていることがわかる。

あとはrtl、xdcディレクトリとセットでtclをgithubに上げるなり、フォルダごとzipファイルにして配布すればOK。

ちなみに、tclからVivadoのprojectを生成する方法はこちらの記事で書いてます。