ZyboのPLブロックでHDMI出力する

前回の日記でBlock Designが完成したので、今回は

- Block DesignからHDL Wrapperを作成してSynethesis

- ピン制約、タイミング制約の設定してImplementation

- Bitstreamを生成してZyboで動かす

について書いていく。

開発環境

Windows 10

Vivado 2020.1

Zybo(Zynq-7000)

Block DesignからHDL Wrapperをつくる

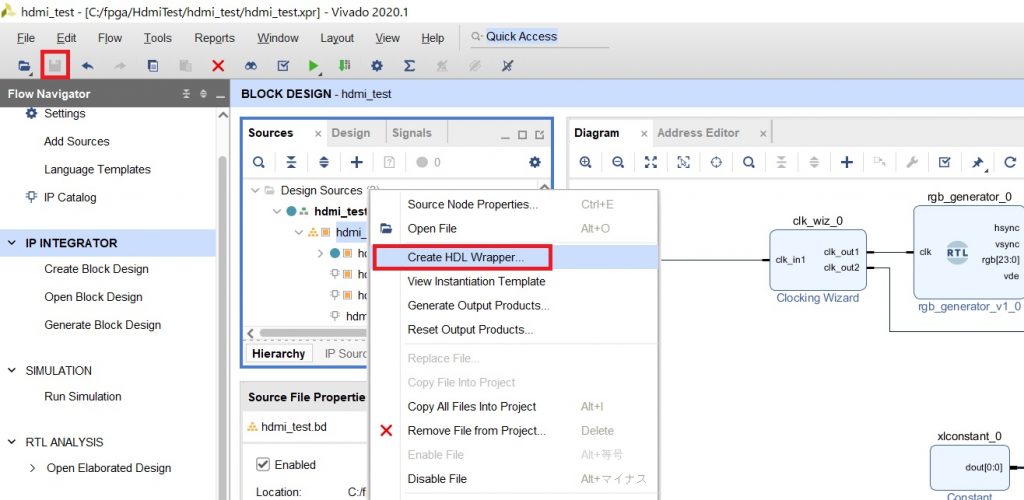

Block Designができたので、あとは通常のBlock Designによる設計フローで手順で進めていくだけ。Block Designを保存したら、SourcesタブのBlock Designを右クリックしてCreate HDL Wrapperをクリック。

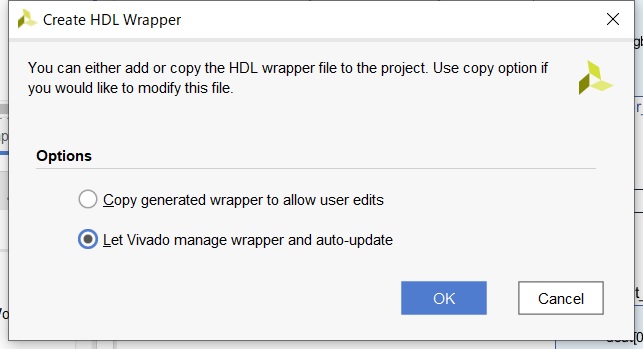

以下のダイアログがでるので、デフォルトのままOKをクリック。

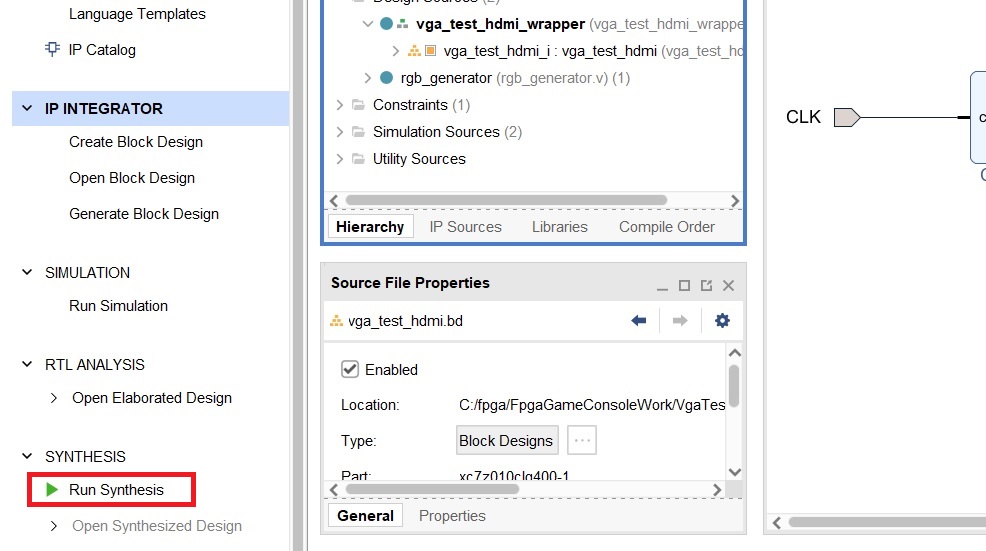

これでしばらく待てばHDL Wrapperができる。これができたらRun Synthesisを実行。

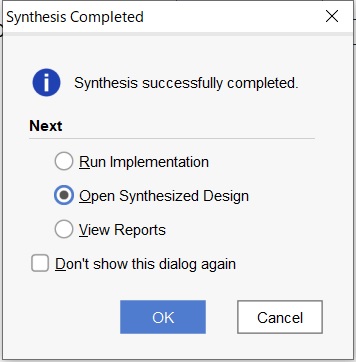

問題なければ以下のダイアログが出てSythesis完了。Open Synthesized Designを開き、ピン制約などを設定していく。

ピン制約、タイミング制約を設定する

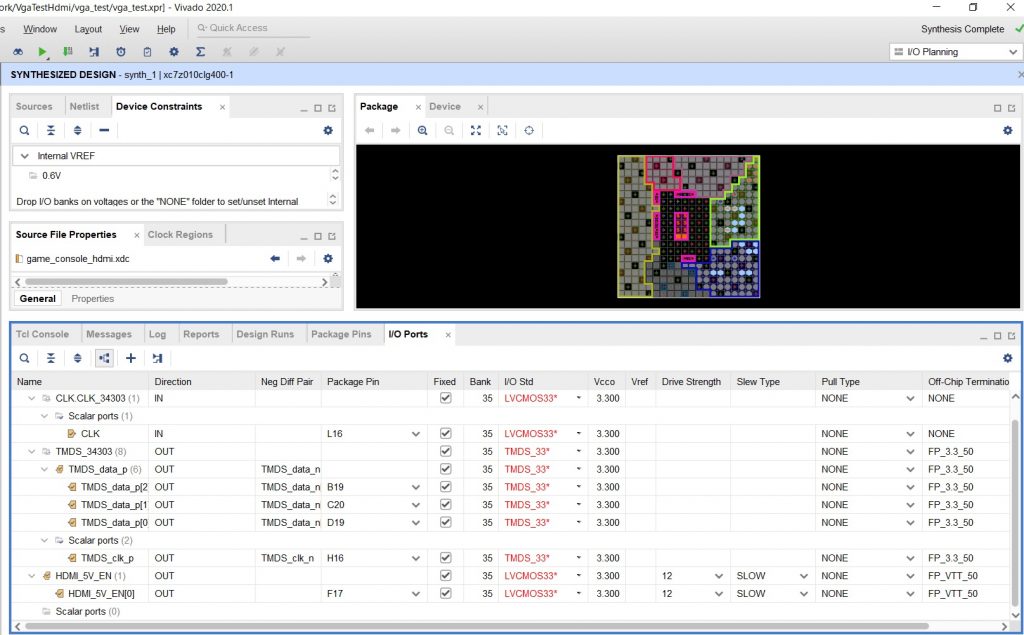

Synthesis Designを開いたら、LayoutからI/O Plannningを選択。

ここで、以下のようにInput/Outputポートを設定する。TMDS出力はI/O StdをTMDS_33に設定する。ちなみに同じZyboでも型番によっては回路図上のピンアサインが違うかもしれないので、自分の持っているZyboの回路図を見てピンアサインを設定してください。

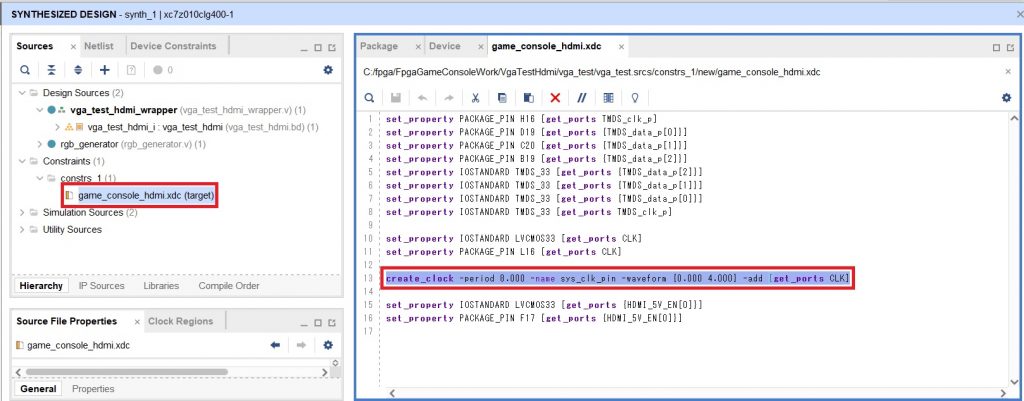

ピンアサインを設定したら、次はクロックの制約を追加する。GUIから設定しても良いが、私はxdcに書いちゃうのが好きなので今回はxdcを開いて直書きする。

Sourcesタブからプロジェクトで(target)に設定されているxdcファイルを開き、以下の画像の赤文字の記述を追加する。私は後からHDMI_5V_ENのピン制約を追加したのでクロック制約がちょっと変な位置に書かれているが、追加する場所はどこでも良いので一番下の行に追加しておけば良い。

追加するのは以下のクロック制約。

create_clock -period 8.000 -name sys_clk_pin -waveform {0.000 4.000} -add [get_ports CLK]

これで入力ピンCLKが8nsecで4nsecごとにhigh/lowが変わる波形(つまり125MHzのクロック)に設定することをツールに教えてあげることになる。今回のHDMI出力ではタイミング関係の制約はこれだけ設定しておけばOK。

実際に動かしてみる

あとはImplementation → Generate Bitstreamを実行してZyboに書き込めばOK。このあたりは何度もやってるので内容は端折るが、詳しい手順はLチカやったときの日記にも書いてるので、やったこと無い人はそちらを参照。

Zyboに書き込み、HDMIケーブルでテレビと接続したところ、以下のようにテストパターンが無事表示された。

ZyboでHDMI出力できた。テレビに認識されねぇ…と思ったら+5Vをhighにしてない初歩的ミスだったのは内緒。Source側の実装はEDID無視できるから楽だな。とりあえず640 x 480/60pとかでだしとけばSinkは受けてくれるし #FPGA pic.twitter.com/ehMBr09d5Z

— Wakky (@wakky_free) May 25, 2021

これでひとまずHDMI出力は完了。次回は、今回のプロジェクトに手を加えて、以前つくったレースゲームのRTLをHDMI出力で動くように変更してみる。

FPGAでゲーム機をつくろう日記まとめ

この日記は以下でまとめています。