いよいよFPGAに実装

以下の本を読みつつ進めているFPGAでゲーム機をつくろう日記。前回はVGAでの映像出力の前編だったの、今回はその続きとして後編を書く。最終的にVGAからテストパターンを出力する。

|

更新頻度からも察して頂けると思うが、丁寧に説明しようと思うと筆が重くなり更新できなくなってきたので(笑)、前回と今回やった内容はGithubの以下のページにプロジェクトごと上げておくので、詳細はこちらを見て頂きたい。

https://github.com/WakkyFree/FpgaGameConsole/tree/master/VgaTest

なお、tclファイルからプロジェクトを生成する方法はこちら。

日記ではポイントだけ絞ってメモしておこうと思う。

開発環境

Windows 10

Vivado 2020.1

Zybo(Zynq-7000)

MMCMで25MHZのクロックを作る

VGAで映像を表示するにあたって、hvsync_generator.v、test_hvsync.vは25MHzのクロックで駆動する必要がある。一方、ZYBOでzynqのPLブロックに接続されているクロックは125MHz。このままだと動かないので、今回はMMCMというIPを使って25MHzのクロックを作る。

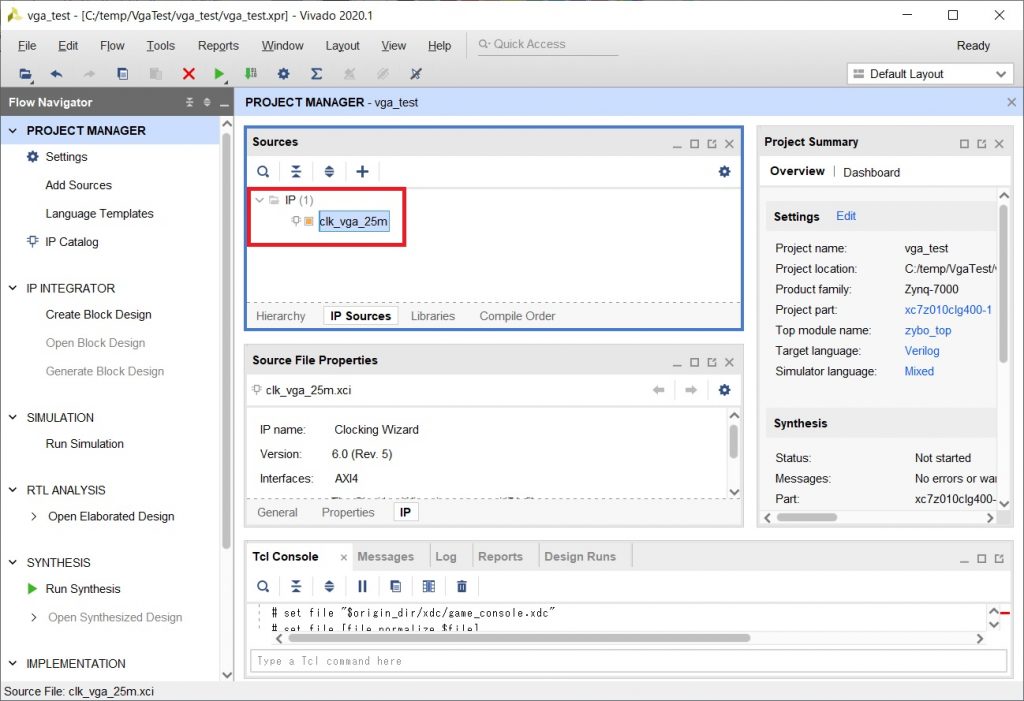

私のgithubのプロジェクトを見てもらうとわかるが、以下のclk_vga_25mというのがmmcmのIP。詳細な設定はダブルクリックで開いてもらえば確認できる。

また、このIPはトップモジュールのzybo_top.vに組み込まれている。

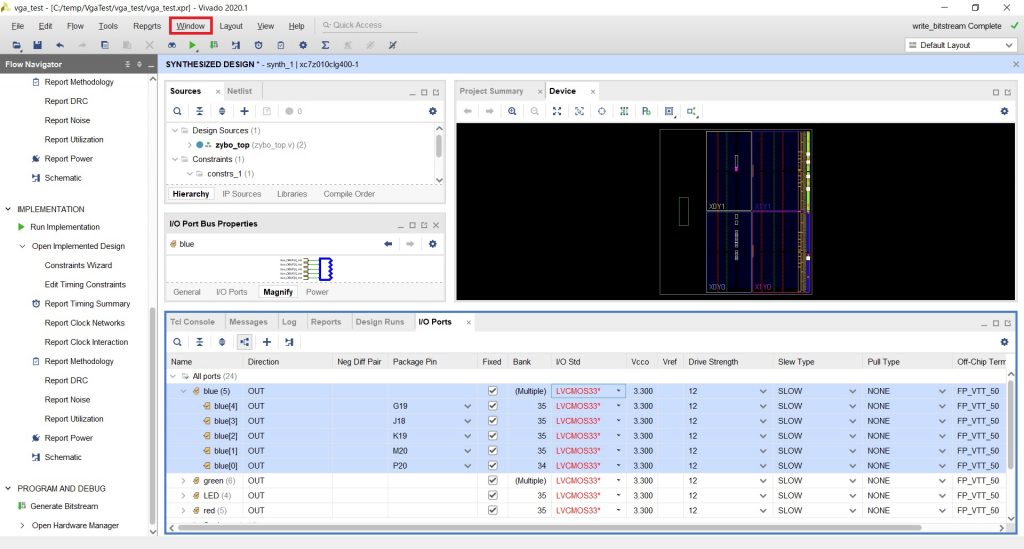

VGAのピンアサイン

次にVGAのピンアサインを行う。私の手持ちのZyboではRed/Blueが5bit、Greenが6bitの階調を表現できるが、今回は簡単にするために1bitのRed/Green/Blueを全部のbitにつなぐ。公開されているZyboの回路図を見つつ、以下のように接続した。こちらはひょっとしたらZyboの世代によってVGAと接続しているピンが異なっているかもしれないので、やる場合は手持ちのZyboの回路図を確認してください。

なお、ピンアサインはプロジェクトをRun Synthesisして開き、「Window」から「I/O Ports」を選択すると確認できる。

このあたりの詳しい手順はLチカやったときの日記にも書いてます。

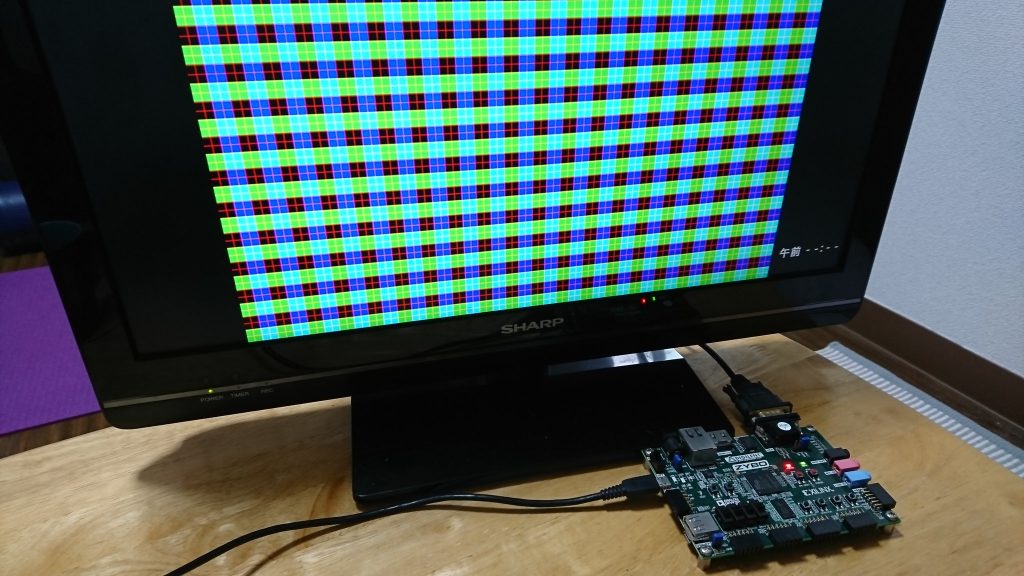

programをwriteして映像出力

このプロジェクトをGenerate Bitstreamまで実行し、Zyboに書き込むと以下のような映像が表示される。

ちなみに、test_hvsync_top.vの中で、以下の記述のvpos/hposのbit数を変えると出力される画が変わる。なんでそうなるかは考えてみてください(丸投げ)

wire r = display_on && (((hpos&7)==0) || ((vpos&7)==0));

wire g = display_on && vpos[4];

wire b = display_on && hpos[4];

これで画の出力はできた。実装はわりと進んでいるのだが、いかんせん日記を書くのが追い付いていない。果たしてそれを日記と呼んで良いものかという疑問もあるが、マイペースに書いていきたい。

次回はもう少しゲームっぽく、moving ballというボールが画面上を動いて、端までいくと跳ね返るという映像の描画サンプルを動かしてみたいと思う。

FPGAでゲーム機をつくろう日記まとめ

この日記は以下でまとめています。