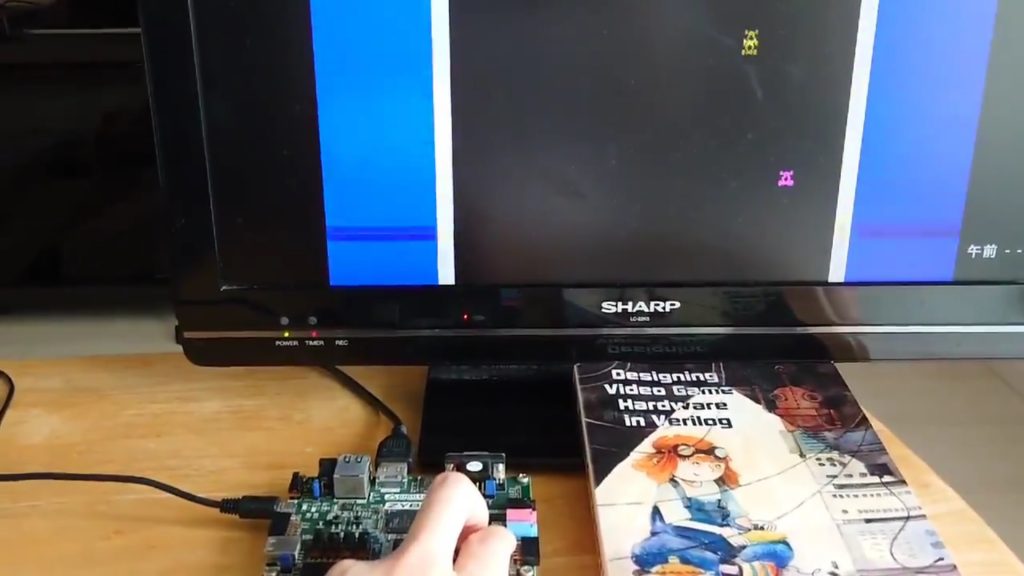

レースゲームをHDMI出力する 前回までの日記で、ZyboのPLブロックを使ってHDMIでテスト映像を出力するところまで書いた。今回は、いよいよレースゲームをHDMIで出力する。といっても、以前作ってVGAで出力していた […]

カテゴリー: FPGA/HDL

【FPGA】ZyboのPLブロックでHDMI映像を出力する:後編 HDL Wrapper生成&制約設定(FPGA + Verilogでゲーム機をつくろう日記9日目)

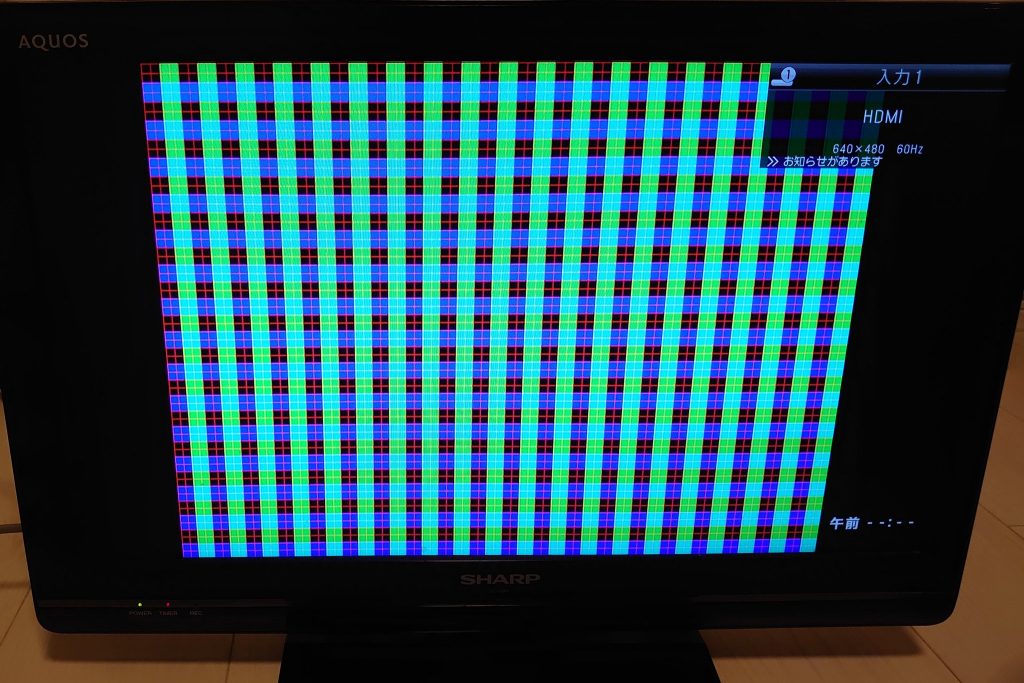

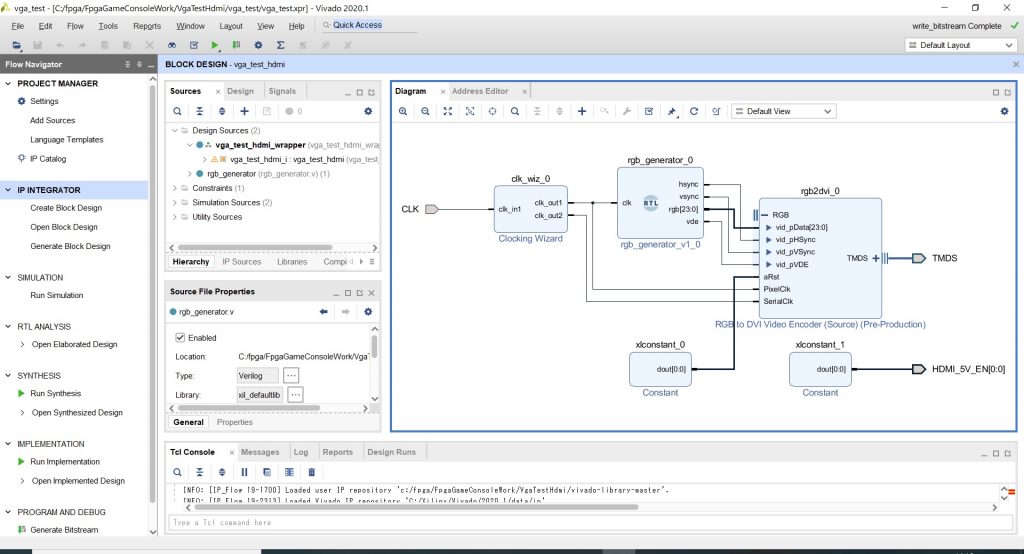

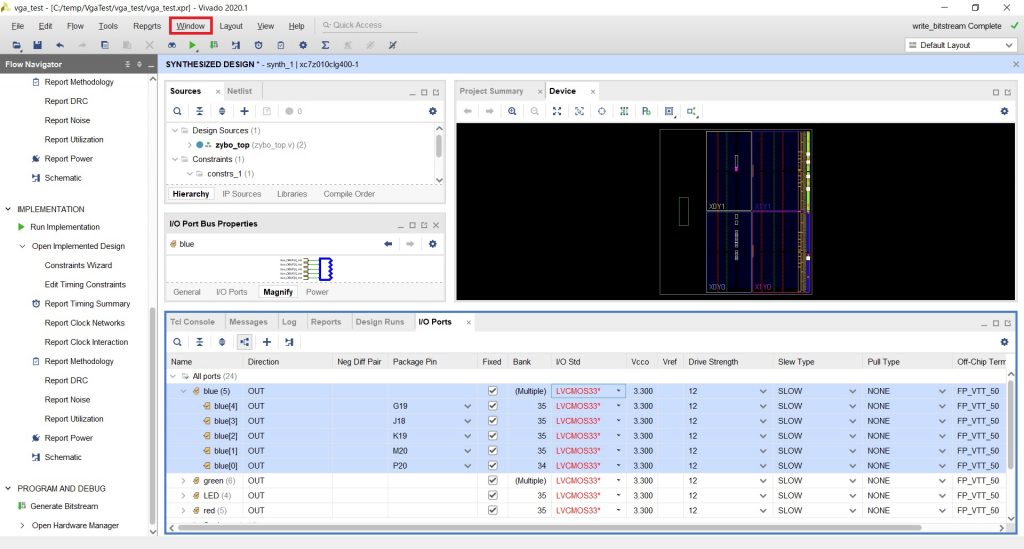

ZyboのPLブロックでHDMI出力する 前回の日記でBlock Designが完成したので、今回は Block DesignからHDL Wrapperを作成してSynethesis ピン制約、タイミング制約の設定してI […]

【FPGA】ZyboのPLブロックでHDMI映像を出力する:中編 IPの追加と設定(FPGA + Verilogでゲーム機をつくろう日記8日目)

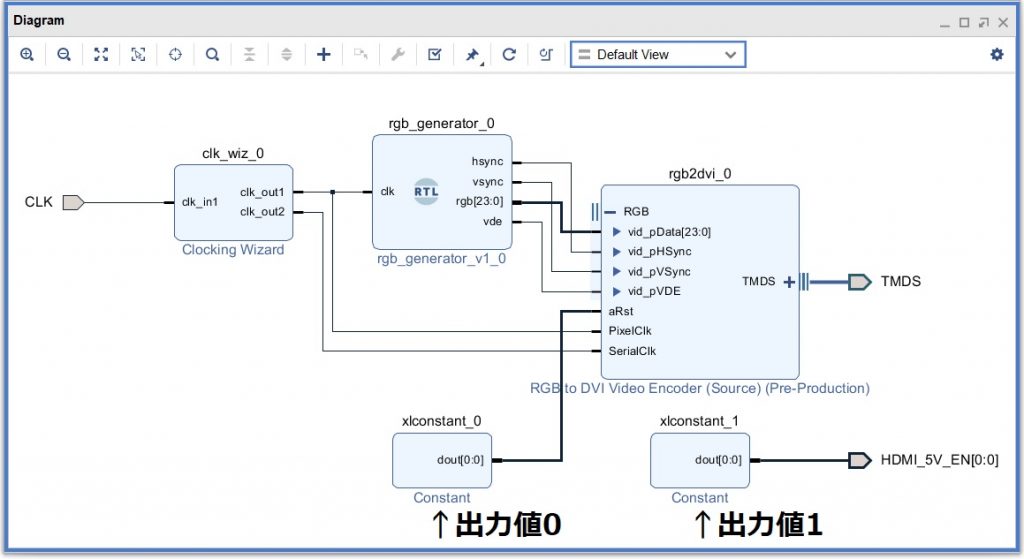

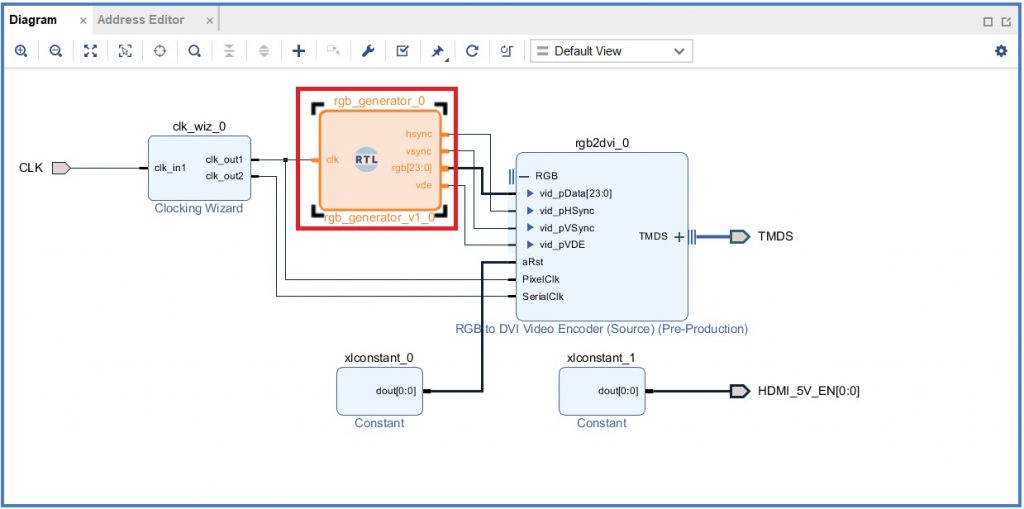

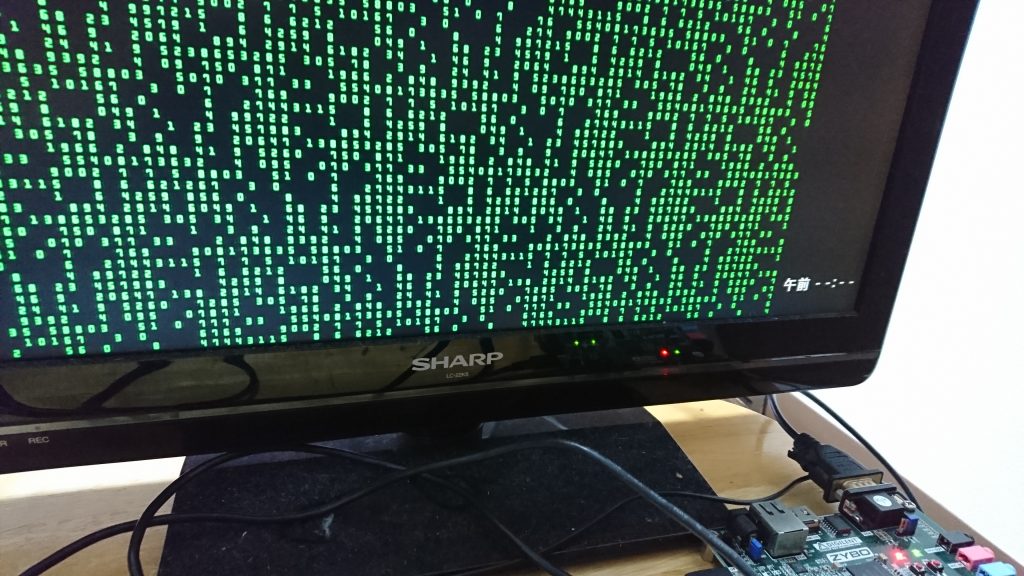

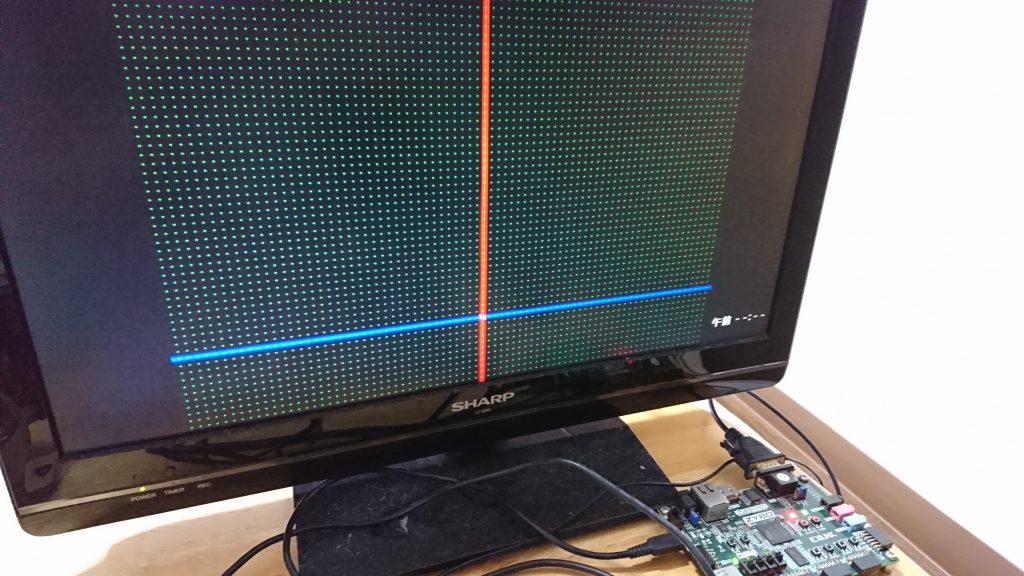

ZyboのPLブロックでHDMI出力する 前回の日記でDigilentのIPのインポート、自作RTL、Input/OutputポートをBlock Designに追加した。今回は DigilentのRGB→DVI変換 IP […]

【FPGA】ZyboのPLブロックでHDMI映像を出力する:前編 IPインポートとIOポート追加(FPGA + Verilogでゲーム機をつくろう日記7日目)

ZyboのPLブロックでHDMI出力する これまでの日記で、ZYBOのPLブロックを使ってRTLで作成したレースゲームをVGA出力する過程を書いてきた。ただ、最近のZYBOはVGA端子が付いてないようなので、HDMI出力 […]

【FPGA】Vivado2020でRTLをBlock Designでモジュールとして使う方法

VivadoのBlock DesignでRTLソースコードをmoduleとして使いたい VivadoのBlock DesignでIPを使うことはよくあるが「自作のRTLソースコードをブロックとしてダイアグラムに追加して使 […]

【FPGA】Racing GameのサンプルをZybo向けに変更して動かす(FPGA + Verilogでゲーム機をつくろう日記6日目)

いよいよRacing Gameのサンプルを実装してゲームを動かす 以下の本を読みつつ進めているFPGAでゲーム機をつくろう日記。前回はtile graphicsというサンプルを実装して動かしてみた。今回はいよいよゲームを […]

【FPGA】Tile GraphicsのサンプルをZybo向けに変更して動かす(FPGA + Verilogでゲーム機をつくろう日記5日目)

今回はTile Graphicsのサンプルを動かす 以下の本を読みつつ進めているFPGAでゲーム機をつくろう日記。前回はmoving ballというサンプルを実装して動かしてみて、だんだんゲームっぽくなってきた。今回は本 […]

【FPGA】Moving BallのサンプルをZybo向けに変更して動かす(FPGA + Verilogでゲーム機をつくろう日記4日目)

今回はMoving Ballのサンプルを動かす 以下の本を読みつつ進めているFPGAでゲーム機をつくろう日記。前回はVGAで画を出力してみた。前回は動きのない静止画を表示したのだが、今回は本の12章「A Moving B […]

【FPGA】VGAでテストパターンを出力:MMCM作成&ピンアサイン設定編(FPGA + Verilogでゲーム機をつくろう日記3日目)

いよいよFPGAに実装 以下の本を読みつつ進めているFPGAでゲーム機をつくろう日記。前回はVGAでの映像出力の前編だったの、今回はその続きとして後編を書く。最終的にVGAからテストパターンを出力する。 Designin […]

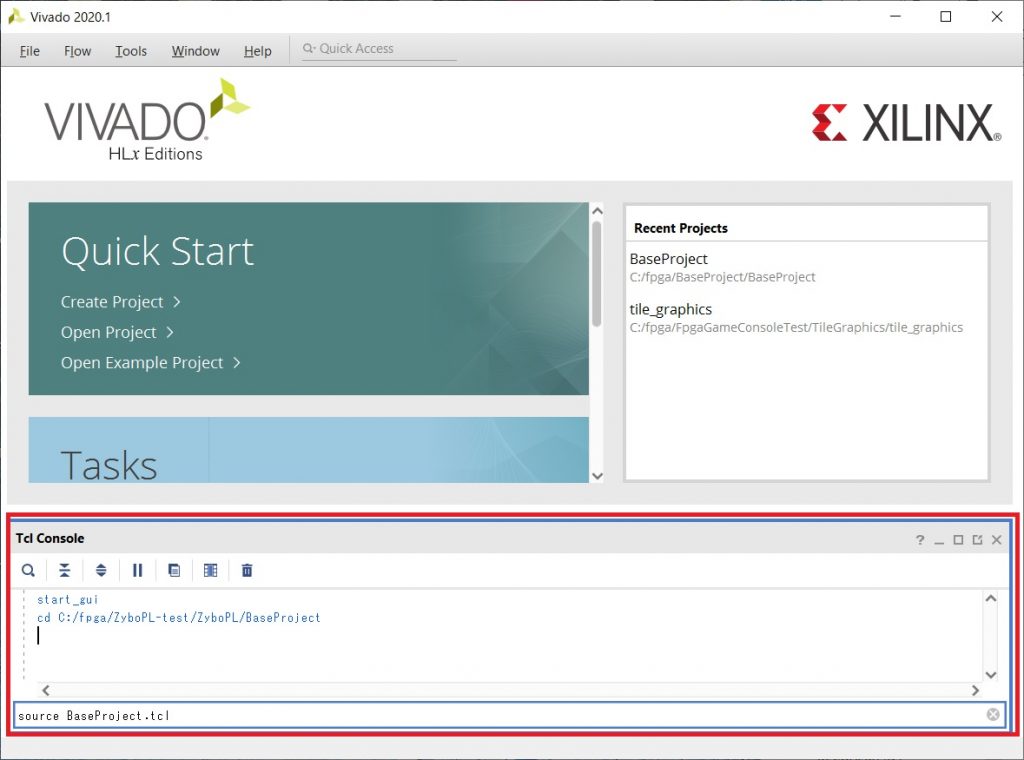

【FPGA】Vivadoのプロジェクトをtclから生成する

Vivadoのプロジェクトをtclから生成する 前回、Vivadoのプロジェクトをtclファイルに書き出す方法を書いた。今回は逆にtclからVivadoのプロジェクトを生成する方法を書いていく。 環境 Wi […]