レースゲームをHDMI出力する

前回までの日記で、ZyboのPLブロックを使ってHDMIでテスト映像を出力するところまで書いた。今回は、いよいよレースゲームをHDMIで出力する。といっても、以前作ってVGAで出力していたレースゲームのRTLをHDMI出力のプロジェクトに移植するだけ。

今回の記事でHDMI出力系はひと段落。

開発環境

Windows 10

Vivado 2020.1

Zybo(Zynq-7000)

HDMI出力のBlock DesignのRTLを置き換える

基本的な流れとしては、前回までで作ったHDMIのテスト映像出力のプロジェクトのRTL部分をレースゲームのRTLに置き換え、ゲーム操作用にZybo上のボタン(タクトスイッチ)をInputポートとして追加する。

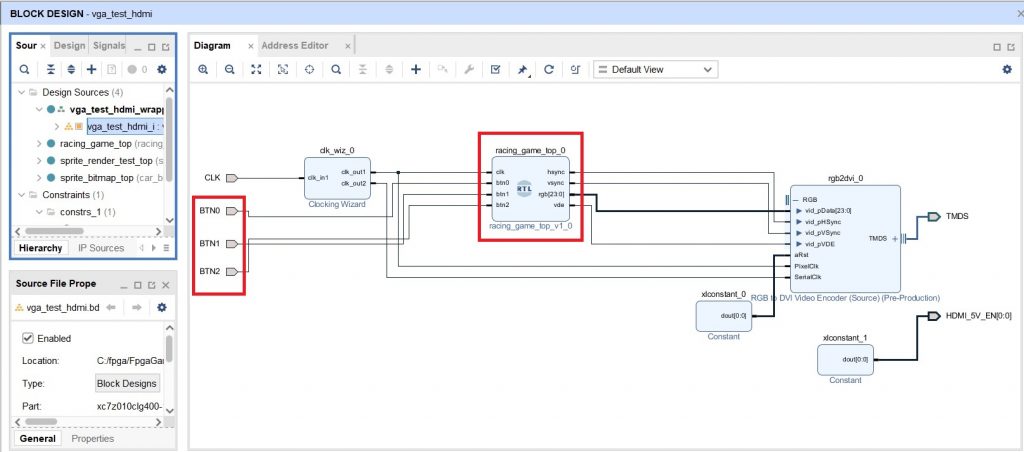

完成系としては以下のようになる。赤枠で囲ったところが今回新たに追加した部分。

racing_game_topのRTLは以下に置いてある。

https://github.com/WakkyFree/FpgaGameConsole/tree/master/HdmiRtls/RaceGame

RTLをBlock Designに取り込む方法は以下を参照。

前回の日記までのRTLコードをこのRTLで置き換え、前回同様に結線する。前回の日記までのRTLとの差分として、ゲームを操作するためのBTN0、BTN1、BTN2があるので、これについては次の節でInputポートを追加して、接続する。

ゲーム操作用のButtonのInputポート&制約追加

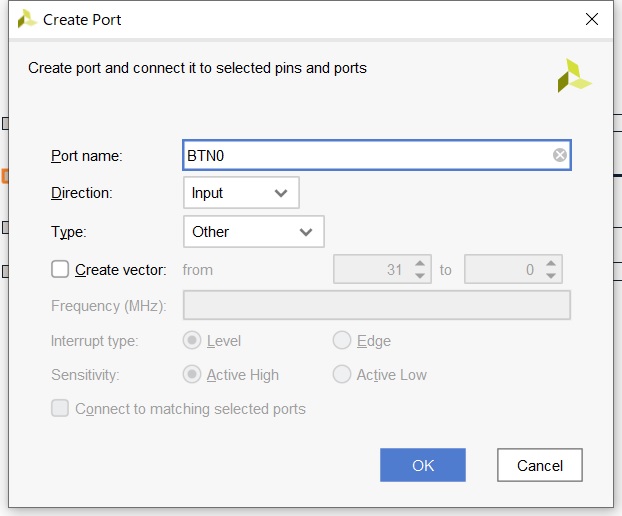

まずは前回と同じ要領で、Block Designの画面で右クリックし、Create Portを選ぶ。以下のようにBTN0~BTN2まで3つのInputポートをt追加する。

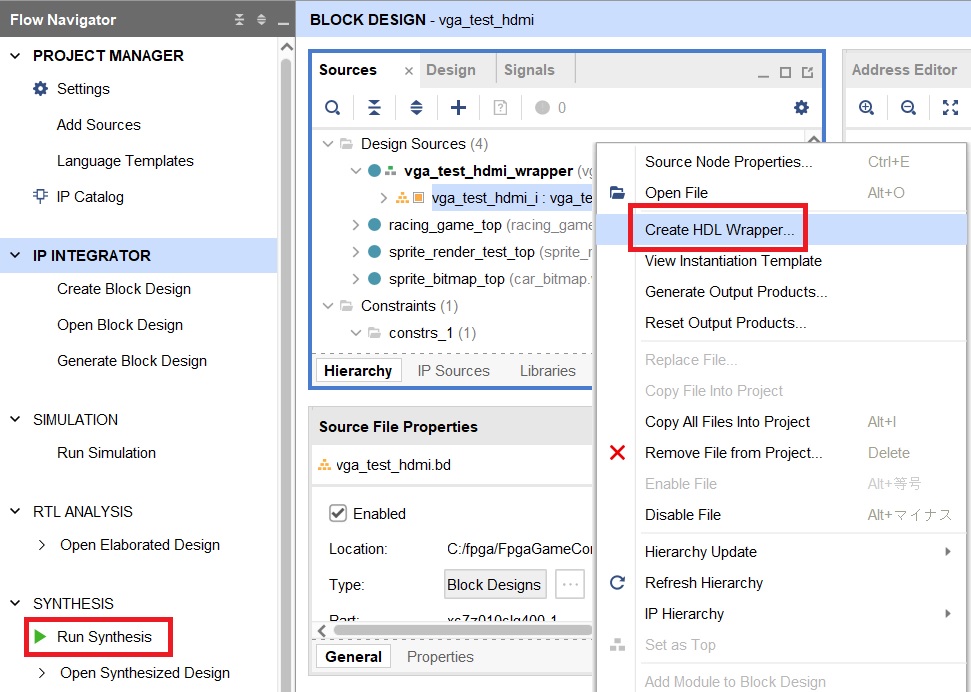

あとはRTLモジュールとBTN0~BTN2を接続すればBlock Designは完成。Block Designを右クリックしてCreate HDL Wrapperを選択し、Run Synthesisを実行して合成する。

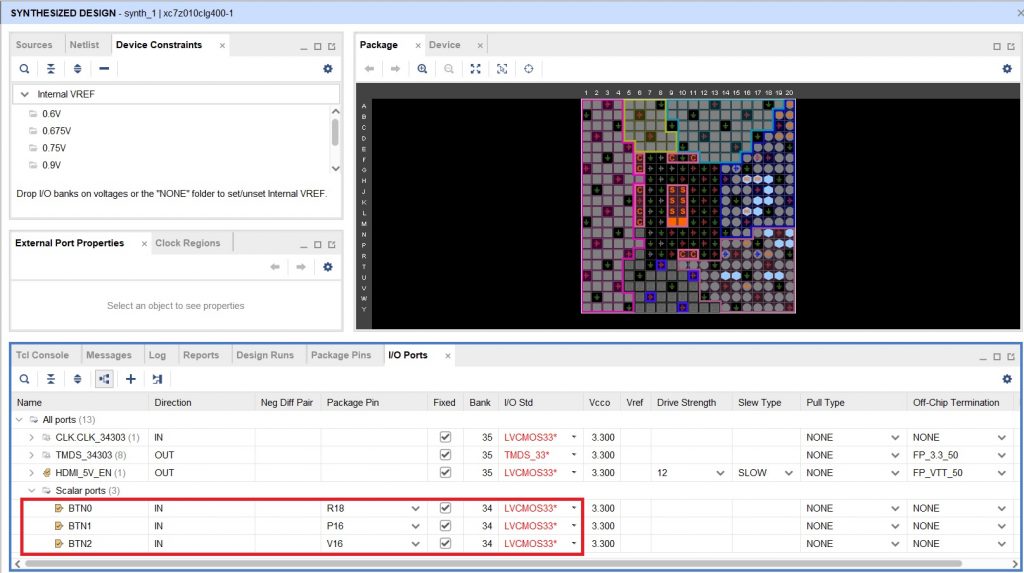

完了したらOpen Synthesized Designを選択して、Layout→I/O Planningを選択してBTN0~BTN2のピンアサインを決める。今回はZyboのタクトスイッチ3つにBTN0~BTN2を割りあてた。同じZyboでも世代によってFPGAと各種スイッチの接続関係が違うかもしれないので、自分が持ってるZyboの回路図を確認してピンを割り当てることをお勧めする。

完了して保存したら、Run Implementation → Generate BitstreamしてからZyboにBitstreamを書き込む。

実際に動かしてみる

これで実際に動かして見ると、以下のように無事テレビとHDMIケーブルで接続してレースゲームが遊べるようになった。

RTLで実装してZyboで動かしたレトロゲームのVGA出力→HDMI出力変更はひっそりと完了した。なおブログ記事は全然追いついてない模様😇 #FPGA pic.twitter.com/cvVBuTEVE0

— Wakky (@wakky_free) June 30, 2021

これでレトロゲームのHDMI出力化は完了した。Zyboでの映像出力系は満足してきたので、次のネタを考え中。やること決めたらまたブログを書いていきたい。

FPGAでゲーム機をつくろう日記まとめ

この日記は以下でまとめています。