Zybo上でGUIのLinuxで立ち上げてみたい

今回は、Zybo上でUbuntu LTS 16.04ベースのXillinuxを立ち上げてみたいと思う。Xillinuxは、Linux/Windows PCでFPGAと通信するIP Core/DriverであるXILLYBUSを利用したLinux Distributionだが、XILLYBUSのIP Coreは評価目的であれば以下からダウンロードしてEvaluation licenseまたは教育用途などであればEducational licenseにより無料で使える。

ただし商用で使う場合などは有料のProduction licenseが必要になるので注意。詳しくは以下のXILLYBUSのライセンスページを参照。

残念ながら現段階ではZyboはサポートの対象外になってしまったようだが、ファイル自体は公開されているので試してみたところ、特に問題なく使えたので手順をメモしておく。Zyboに入れるためにあれこれと操作を行う母艦PCはLinuxでやるケースが多いと思うし、私も一応Linux環境は持ってるのだが、今回はあえてWindows10からやってみる。

開発環境

母艦PC:Windows 10

Vivado 2020.1

Zybo(Zynq-7000、型番410-279)

ファイルをダウンロードして解凍する

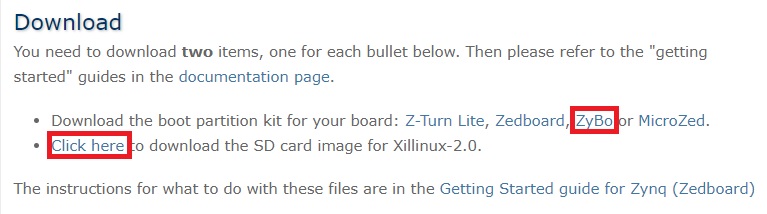

基本的にはこちらの公式ドキュメントを読みながら進めていく。まずはダウンロードページの以下のリンクから2つファイルをダウンロードする。

zybo用のファイルの方(xillinux-eval-zybo-2.0d.zip)はzipなのでWindowsデフォルトのソフトで解凍すれば良いが、Xilliuxのイメージ(xillinux-2.0.img.gz)の方は.gzで圧縮されている。Linux PCであればgunzipコマンドを使って解凍するが、Window PCでも7zipなどの解凍ソフトを使えば解凍できる。

xillinux-2.0.imgはSDカードに書き込むイメージだが、まずはxillinux-eval-zybo-2.0dのファイルからVivadoのプロジェクトを作成して、generate bitstreamを実行する。

Vivadoでtclファイルからプロジェクトを作成&generate bitstreamを実行

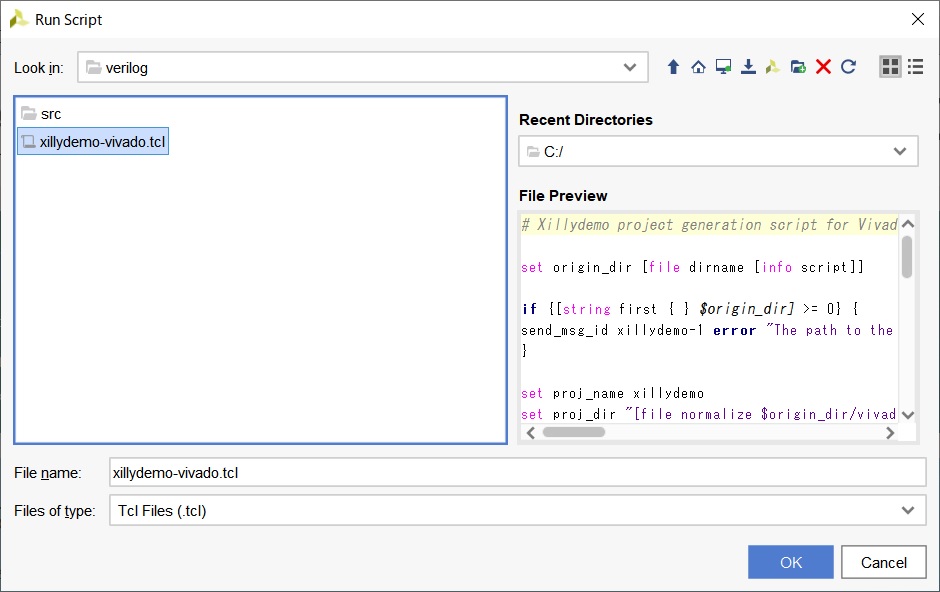

xillinux-eval-zybo-2.0d.zipを解凍して、フォルダの中のtclファイルからVivadoのプロジェクトを作成するのだが、フォルダにはVerilogとVHDLの2つのファイルが入っており、どちらか選択してプロジェクトを作成する(動作には特に違いはないと思う)。私は普段Verilogを使っているので、今回はVerilogでプロジェクトを作成して進めることにした。

公式ドキュメントの「3.2 Unzipping the boot partition kit」に従い進めていくが、xillinux-eval-zybo-2.0dのパスに空白(スペース)が含まれているとダメらしいのでxillinux-eval-zybo-2.0dを置く場所に注意。迷ったらCドライブ直下などに置いておけば問題ないはず。今回使うのは以下のtclファイル。

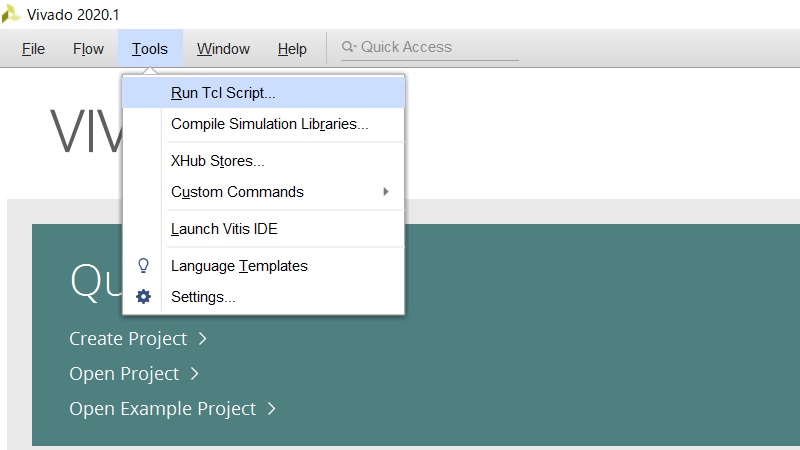

Vivadoを立ち上げて、ToolsからRun Tcl Scriptを選択。私はVivado 2020.1を使ったが、Webサイトを読むとVivado 2016.4以降ならOKとのこと。

xillinux-eval-zybo-2.0dの中からverilogフォルダのxillydemo-vivado.tclを選択してOKをクリック。

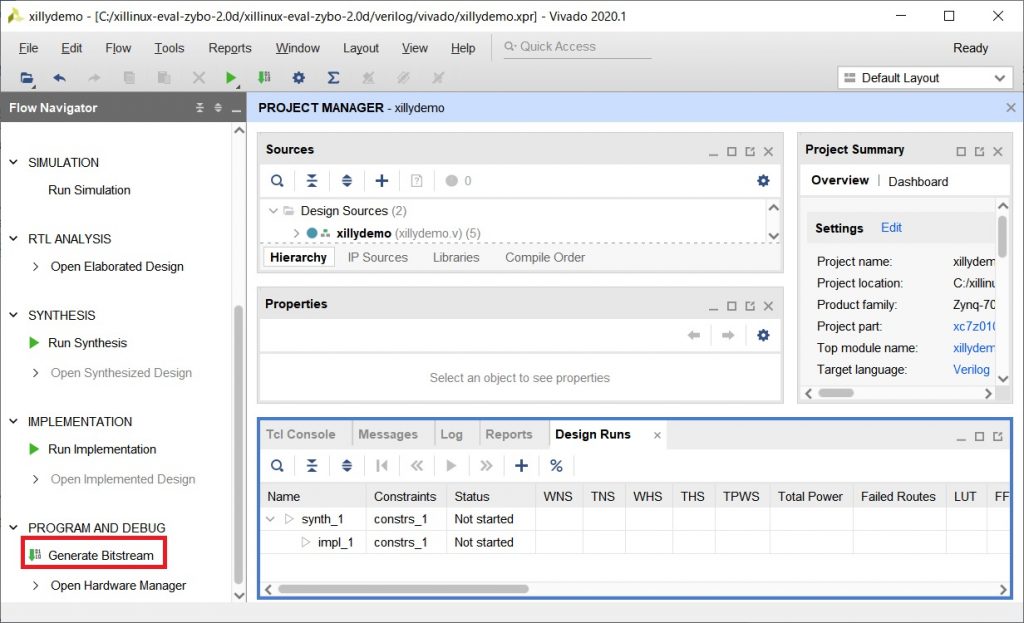

これで特に問題なくプロジェクトが開けるはずなので、Generate Bitstreamを実行。

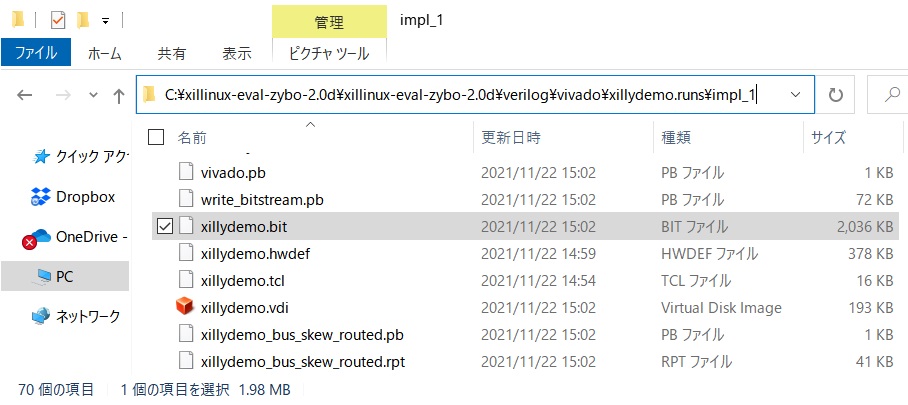

問題なく通ればerrorは出ずに、xillydemo.runs\impl_1フォルダの中にxillydemo.bitファイルが作成される。このファイルがxillinuxを起動するときに必要になる。

これで準備は完了。いよいよSDカードにイメージを書き込んで必要なファイルをコピーしてXillinuxを立ち上げる。長くなったので続きはこちら。