この日記でやること

今まで高位合成(※)に触れようと思いつつ、なかなか機会が無かった。そこで今回は、Xilinx社のVivado HLSというツールで高位合成にチャレンジしてみようと思う。以前は有料ライセンスが必要だったが、現在は無料で使用できる。RTLを生成するだけで終わり、だとつまらないので、生成したVerilogのコードをZyboのPLブロックに組み込んで、LEDを点滅させてみる予定。

具体的には、以前書いた「FPGAのPLブロックだけを使ってLチカ日記」のRTLで、Microblaze MCSのRTL topモジュールにVivado HLSで生成したRTLを組み込んでみる。イメージとしては、下の図の赤文字の部分をHLSでつくる。色々と細かく厳密なことを書くより、シンプルに最低限の手順で高位合成する方法を書く方針で進めていきたい。

※高位合成(High Level Synthesis):アルゴリズムからレジスタ転送レベル(RTL)の回路を自動で合成する技術。現状ではC言語などで記述されたアルゴリズムをVerilogやVHDLに変換するのが主流。

環境

Windows 10

Vivado HLS 2018.3

ZYBO

プロジェクトを作成

Vivado HLS 2018.3を起動し、Create New Projectをクリック。

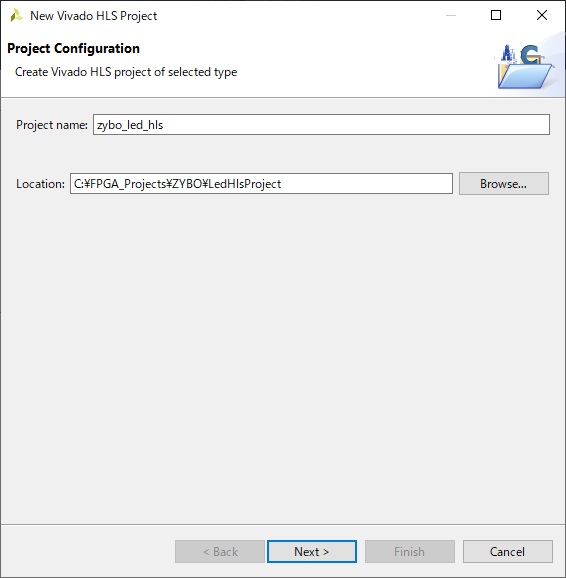

プロジェクト名は適当に「zybo_led_hls」とかにしておく。Locationもプロジェクトをつくりたいディレクトリを適当に指定する。

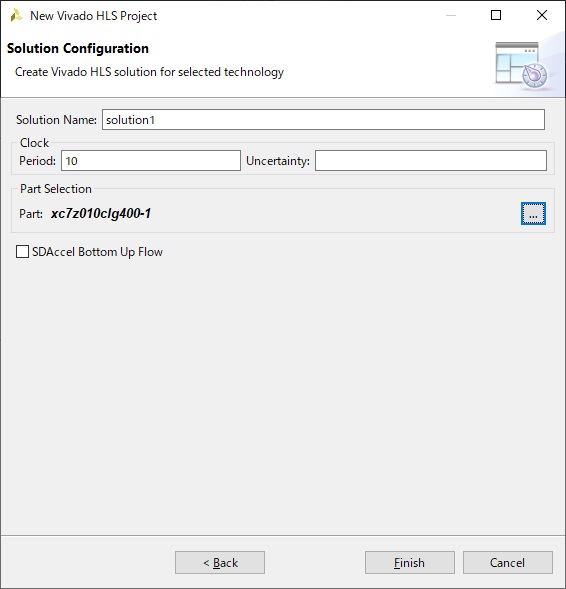

次のTop FuncitionとTestBench Filesはおいおい書いていくので、とりあえず空白のまま「Next」を押して進む。最後のSolution NameはデフォルトのままでOKだが、Partから対象のFPGAを選択する必要がある。ということでPartの右側の「…」をクリックする。

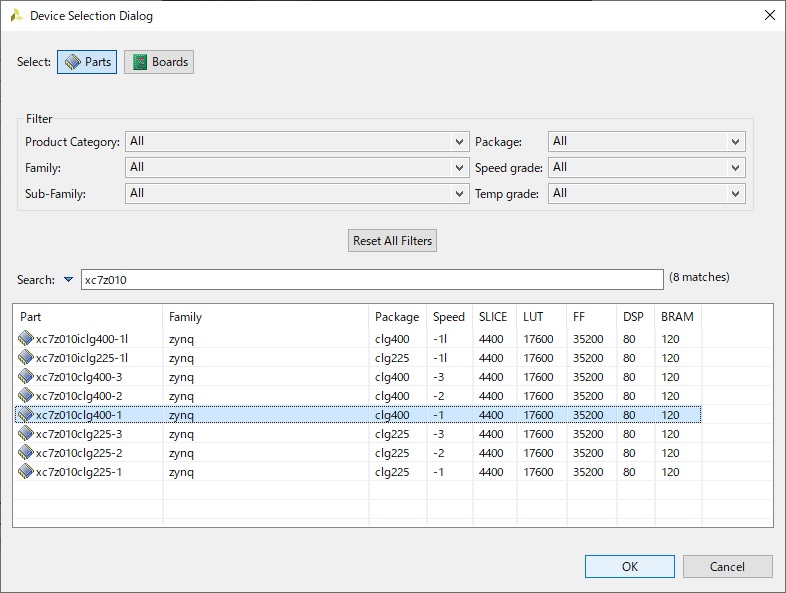

ZYBOに搭載されているZynq(xc7z010clg400-1)をSerchから検索し、選択してOK。

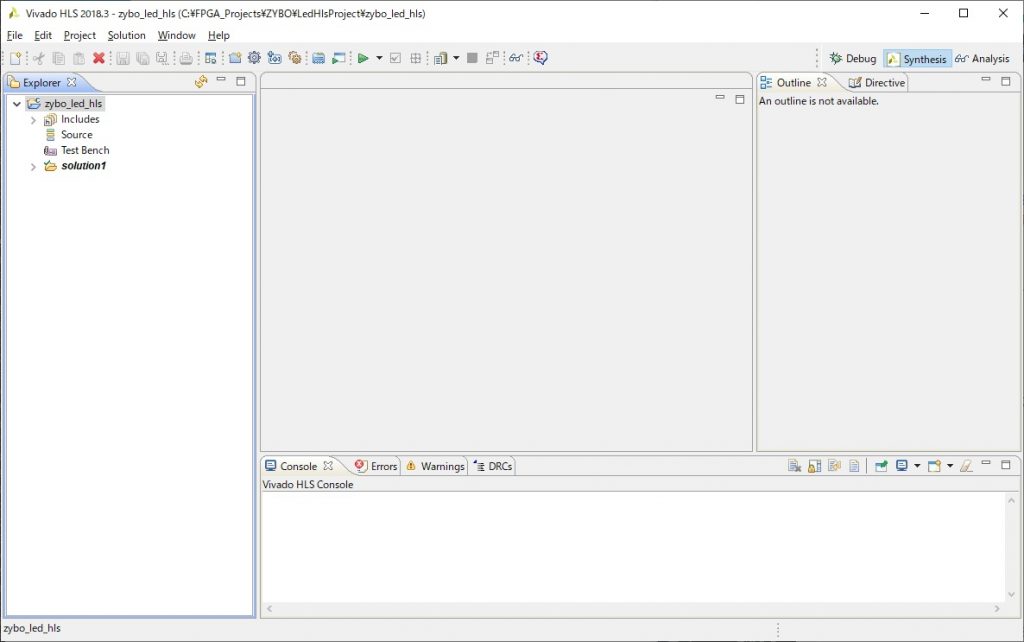

これでFinishを押せば完了。無事にVivado HLSが立ち上がった。

次回はC言語のコーディングをやってみる。

参考文献

公式のドキュメントが以下にあるので、参照しながら進めていきます。

UG871:Vivado Design Suite Tutorial – Hi-Level Synthesis

UG902:Vivado Design Suite User Guide – Hi-Level Synthesis

以下の資料も参考にさせて頂きました。

https://www.slideshare.net/marsee101/vivado-hls1

ZYBOで遊ぼう日記まとめ

ZYBO関係の記事は、大まかな内容ごとに以下にまとめています。

https://wakky.tech/zybo/