今回やること

前回はVivadoを最新版にして力尽きたので、今回からやっと本題のMicroblaze MCSに入っていく。まずは既存のLチカRTLに、Microblaze MCSのIP Coreを組み込んでいく。

環境

Windows10

Vivado HLx 2018.3: WebPACK

ZYBO

Microblaze MCSを新規作成

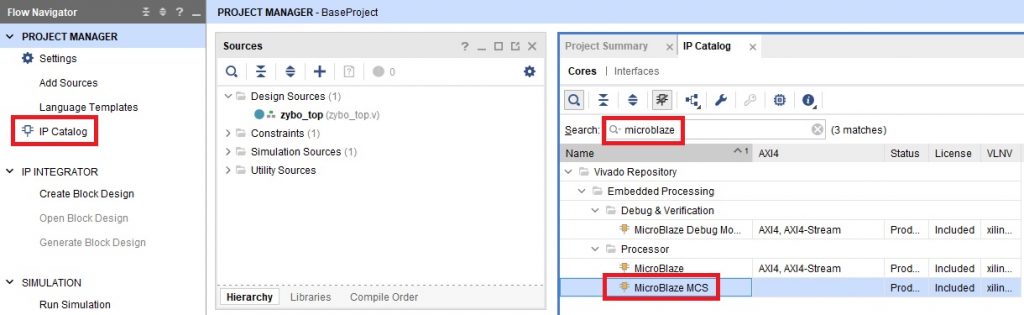

まずは、IP CatalogからMicroblaze MCSを作成する。下の画像のように、Microblazeで検索すれば出てくるので、ダブルクリックする。

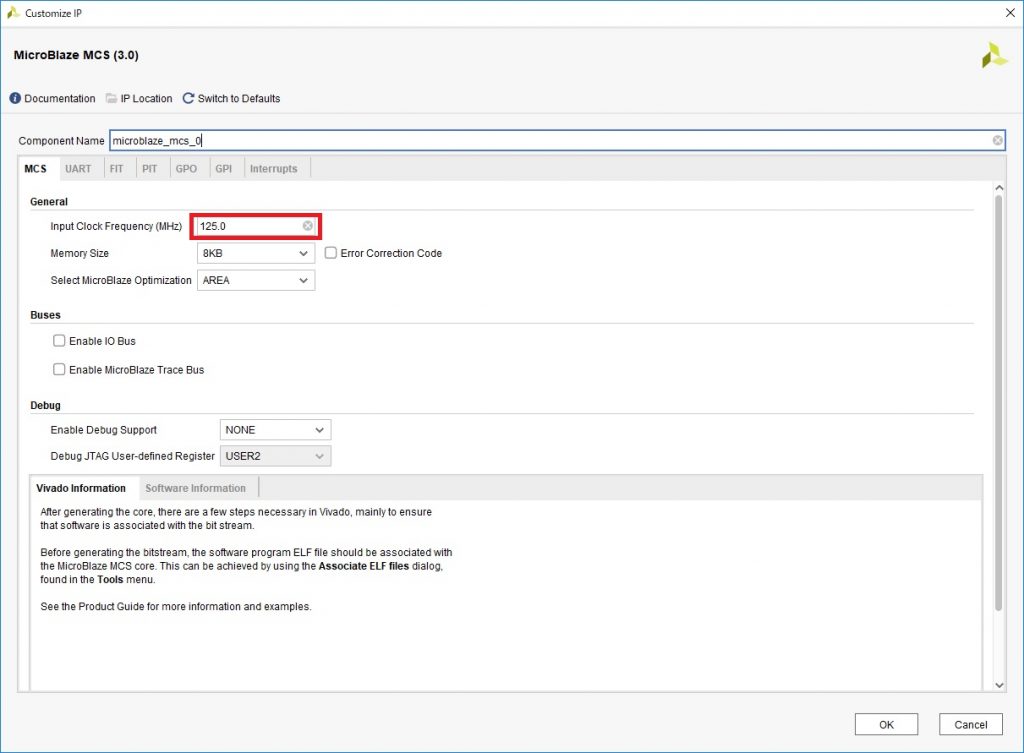

Microblaze MCSの設定画面が出てくるので、周波数をZYBOの125MHzに設定。

追記:画像では「Debug」の「Enable Debug Support」がNONEになっていますが、ここをDEBUG&UARTに変更しておいてください。変更しないと、最後にJTAGでソフトウェアを書きこむときにErrorが出ます。これについては日記の最後にデバッグ編として紹介する予定なので、あえてこのままにしています。

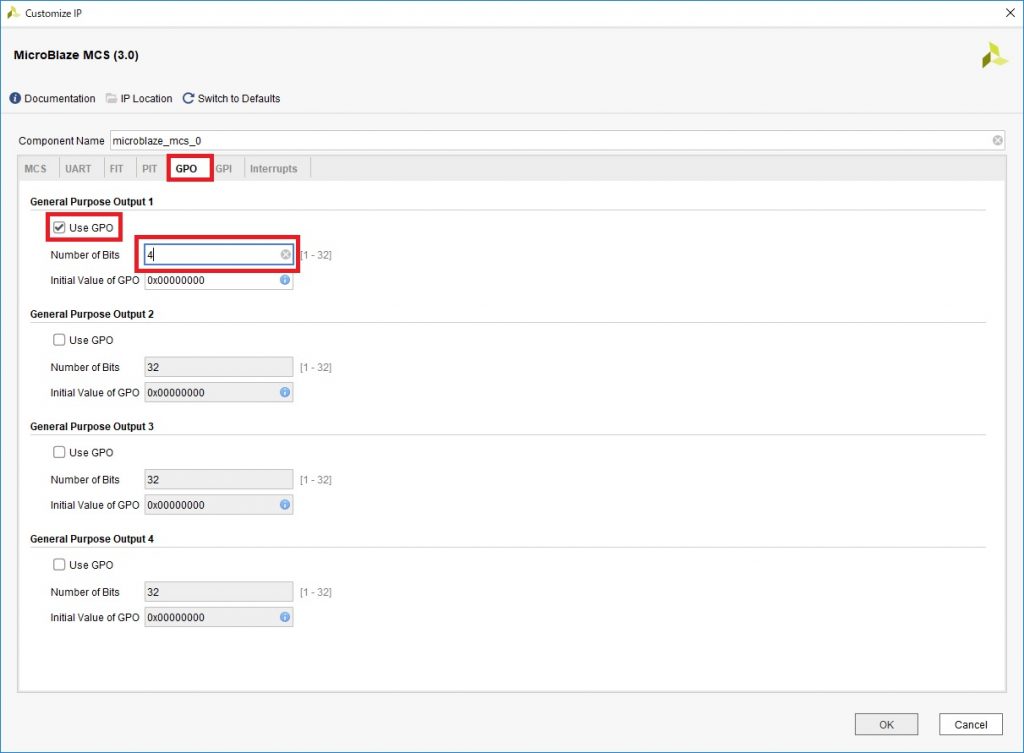

次にGPOタブを選択する。Zynqに接続されたLEDは4つあるので、それぞれ別個に制御できるようにbit幅を4に設定する。

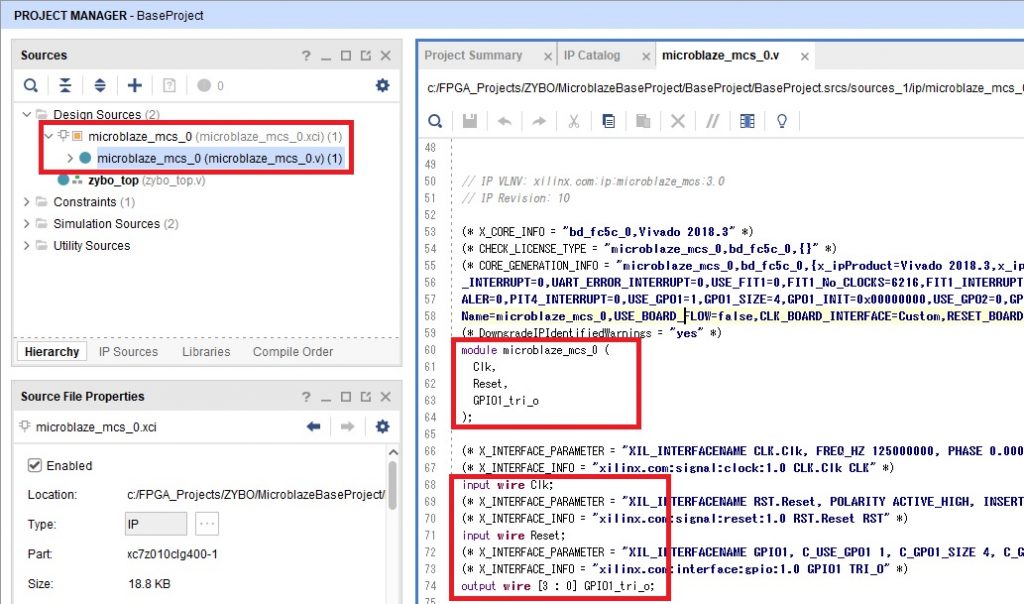

これで設定は完了。思ったより簡単だった。後はデフォルトのままOKを押していき、Generateを押せばIPが生成される。生成されたIPはmodule化されて、IPファイルの中のverilogファイルでmoduleのinput/outpuポートを確認することができる。

Microblaze MCSをトップモジュールに組み込む

以前verilogで作成したトップモジュールMzybo_top.vの中のLEDを点滅させたコードをコメントアウトし、以下のように変更した。MicroblazeからのGPOをLEDに接続し、制御できるようにしている。

この状態でSynthesis、Implementation、Generate Bitstreamを実行すれば、ハードウェアは完成。思ったより簡単だった。次回はMicroblaze MCSのGPIOを制御するファームウェアを作成して、LEDを光らせる。

参考文献

公式のドキュメントが以下にあるので、参照しながら進めてます。

https://japan.xilinx.com/support/documentation-navigation/design-hubs/dh0020-microblaze-hub.html

ZYBOで遊ぼう日記まとめ

ZYBO関係の記事は、大まかな内容ごとに以下にまとめています。

https://wakky.tech/zybo/