ZyboのPLブロックでHDMI出力する

前回の日記でDigilentのIPのインポート、自作RTL、Input/OutputポートをBlock Designに追加した。今回は

- DigilentのRGB→DVI変換 IPの追加&設定

- 入力ClockからHDMI出力に必要なclockをつくるMMCMの追加&設定

- DigilentのIPへのリセット入力やHDMI_5V_EN出力で使う固定値をBlock Desginに追加

まで書いていく。

開発環境

Windows 10

Vivado 2020.1

Zybo(Zynq-7000)

IPを追加&設定する

DigilentのRGB→DVI変換 IP(rgb2dvi)を追加

まず、Digilent社のRGB→DVI変換IPを追加する。HDMIは規格的にDVIへの下位互換があるので、DVI出力すればHDMIでも画が出る(はずだが、Sink機器との接続問題で出なかったりするケースもある)。

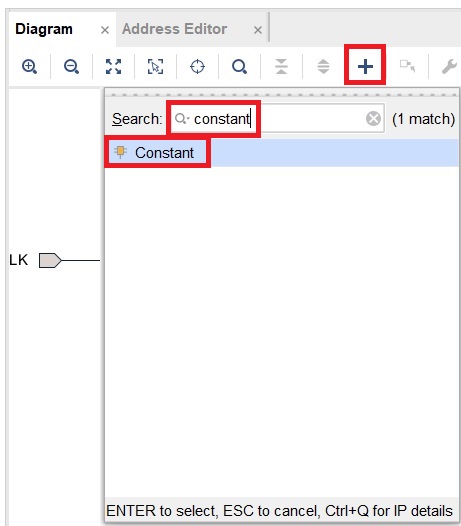

まずBlock Diagramを開いてBlockタブの以下のボタンを押し、RGB to DVIと検索する。前回の日記の内容通りDigilentのIPをインポートしていれば、以下のように出てくるはずなのでSourceの方をダブルクリックする。

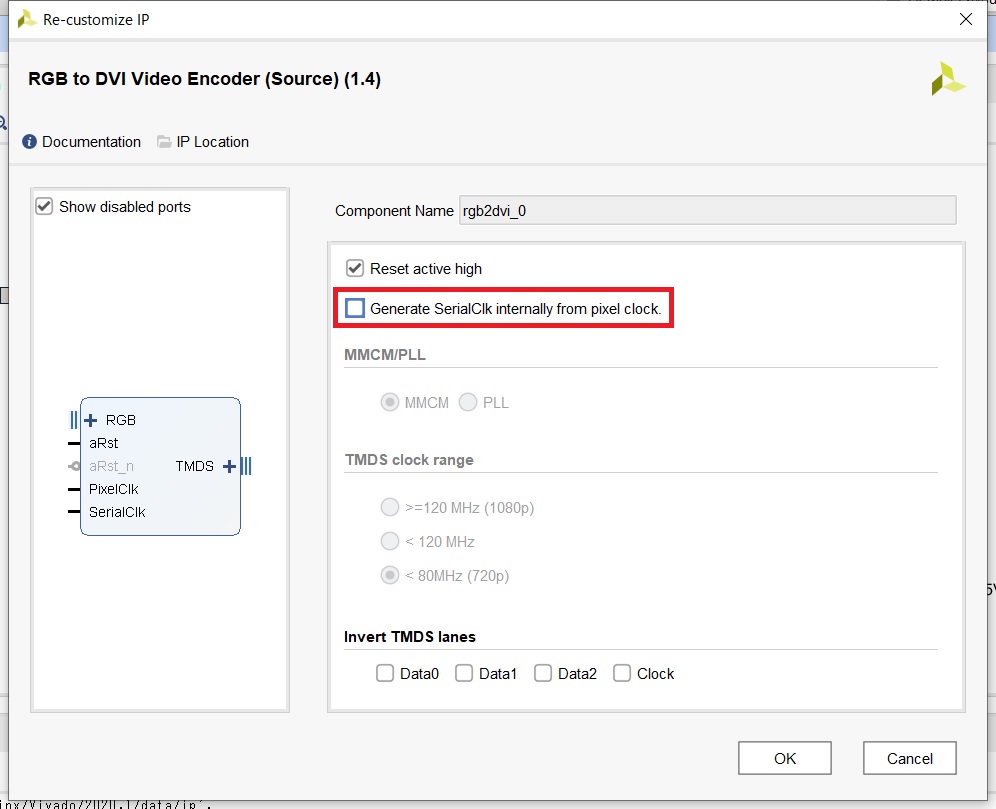

するとBlock Diagram上にIPが配置されるので、配置されたブロックをダブルクリックして設定していく。RGB to DVI EncorderではPixel ClockとSerial Clockの2種類が必要だが、Serial ClockはIPの内部で生成することができる。…のだが、Serial Clockを内部で生成したらSynthesisの時にErrorが出てしまったので、今回は外部から入力することにした。ということで、以下のように「Generate SerialClk internally from pixel clock」からチェックを外してOKをクリック。グレーアウトされている部分の設定は反映されないので、何でも良い。

MMCMを追加する

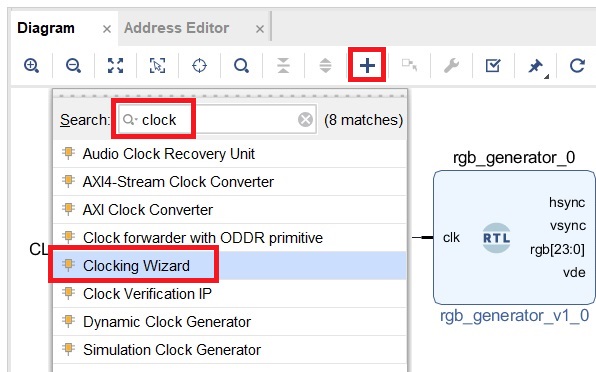

次に、入力クロックからPixel ClockとSerial Clockをつくるために、MMCMを追加する。先ほどと同じ要領でIPの検索で「Clock」と入力し、「Clock Wizard」をダブルクリック。

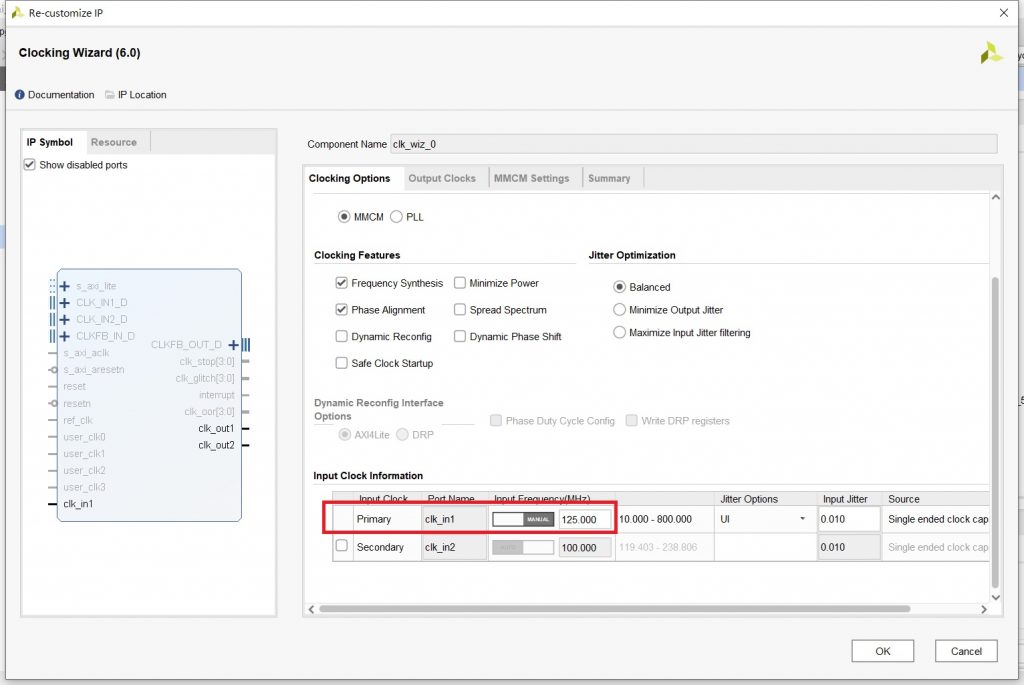

追加したらブロックをダブルクリックして、以下のようにMMCMを選び、InputクロックはPLブロックに入力されているクロック125MHzに設定する。

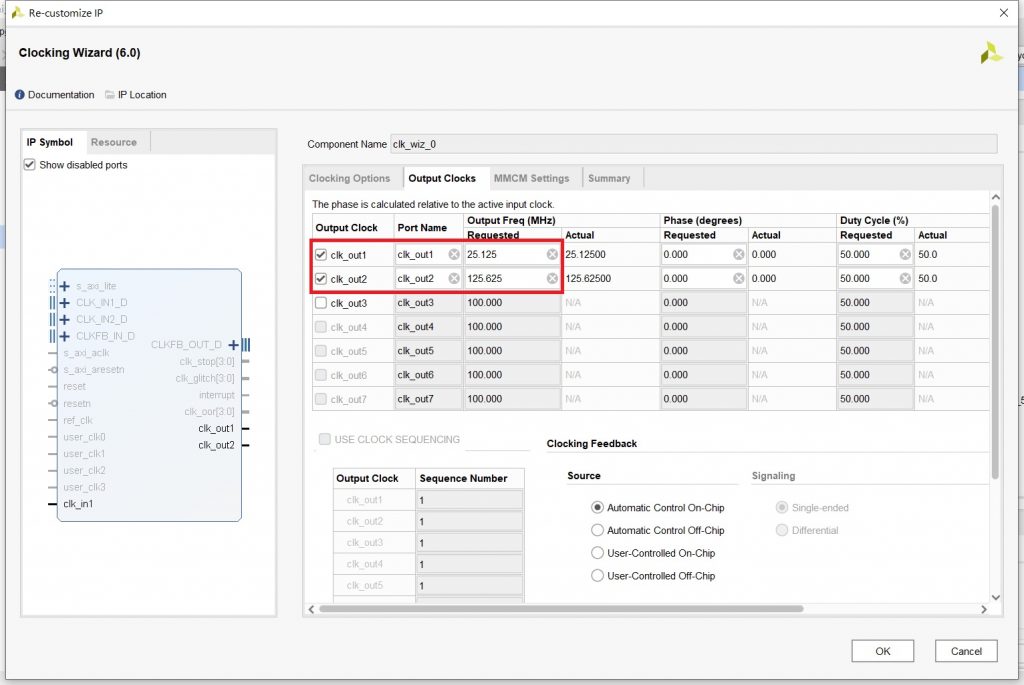

今度は出力クロックの設定。今回は640 x 480/60pでHDMI出力するので、Pixel Clockは25.125MHzとなる。Serial Clockはその5倍なので、125.625Mhzに設定する。Pixel Clockは解像度やフレームレートによって異なるので、もし違う解像度に改造する人はこのあたりを参考にしてもらうと良いと思う。

Constant(定数)を追加する

前回の日記で追加したOutputポートのHDMI_5v_ENは、FPGAがconfigurationされたら常時HIGHにしておけば良い。ということで、Constant(定数)のIPを使ってHIGH固定値にしておく。これまでと同じ要領で、constantでIP検索して、出てきたIPをダブルクリック。

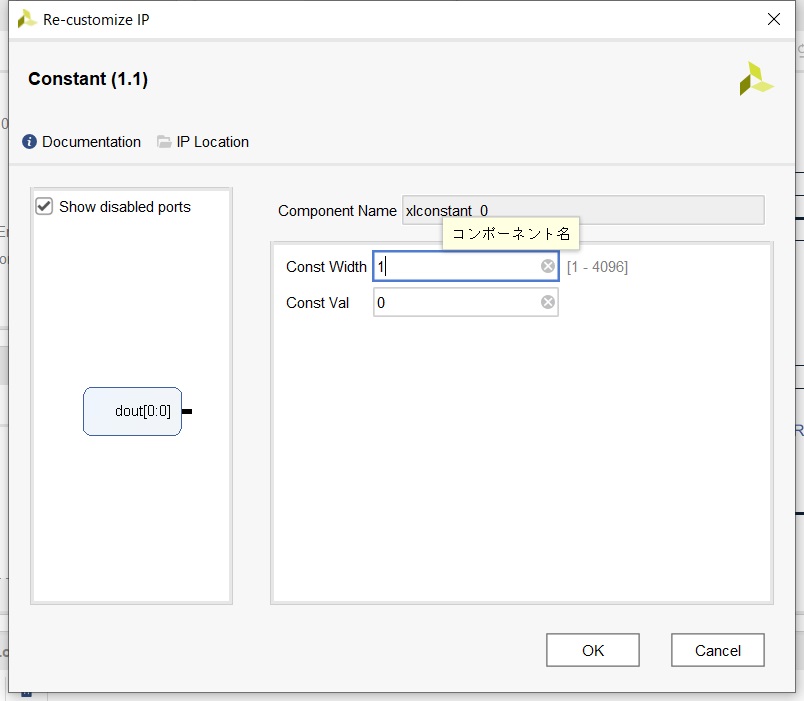

追加されたブロックをダブルクリックして、以下のように1bitで出力値1に設定する。

また、RGB to DVI EncorderのリセットをLOWに固定しておくため、もうひとつConstantを配置しておく。配置したら以下のように1bitで出力値0に設定。

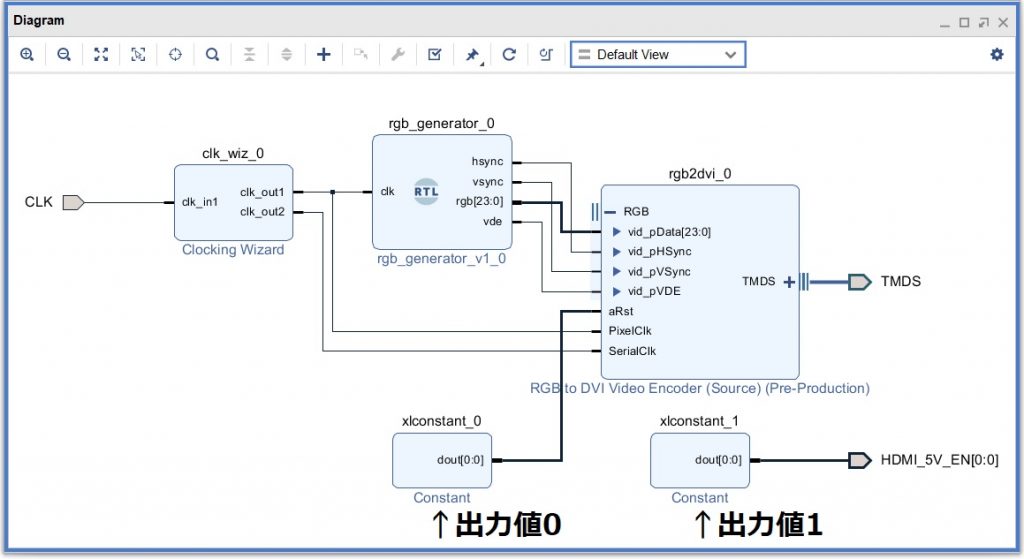

これでBlock Designに必要なものは一通り置けたので、以下のように配線する。出力値0と1のConstantの配線を間違えないように注意。(ここまで書いてて思ったけど、rgb2dviのResetの極性を設定で反転させてれば、出力値1のConstantだけにできた…まぁいいか)

あとは通常のフローでHDL Wrapperを作ってピン&クロックの制約追加をしてSynthesis→Implementation→Generate BitstreamしてZyboで動かしてやる。続きは次回。

FPGAでゲーム機をつくろう日記まとめ

この日記は以下でまとめています。