ZyboのPLブロックでHDMI出力する

これまでの日記で、ZYBOのPLブロックを使ってRTLで作成したレースゲームをVGA出力する過程を書いてきた。ただ、最近のZYBOはVGA端子が付いてないようなので、HDMI出力する方法も書いた方が需要はありそう。ということで、今回はZyboのPLブロックを使ってHDMI映像を出力する方法をまとめていく。最終的にはゲームをHDMI出力で遊べるようにするけど、ひとまず今回はテスト画像を出力するところまで書く。ちなみに最終形は以下のようになる。

ZyboでHDMI出力できた。テレビに認識されねぇ…と思ったら+5Vをhighにしてない初歩的ミスだったのは内緒。Source側の実装はEDID無視できるから楽だな。とりあえず640 x 480/60pとかでだしとけばSinkは受けてくれるし #FPGA pic.twitter.com/ehMBr09d5Z

— Wakky (@wakky_free) May 25, 2021

これまでの日記だとプロジェクトをtclファイル化していたが、今回はDigilent社のHDMI出力IPを使ったりブロックデザインを使ったりしておりtcl化するとライセンス関係がややこしいし単純に面倒なので、ブロックデザインと各IPのパラメータ、module化したRTLのコードなどポイントだけ載せておく。ある程度ZYBOのPLブロックをRTLで動かしたことがある人なら、読めばわかると思う。

一応ベースとなるのはこちらの日記で作成したVGA出力のプロジェクトだが、プロジェクトを改造するとトップモジュールの変更など必要になったりするので、慣れていない人は一からプロジェクトをつくりなおした方が良いかも。ZYBO用のプロジェクトを新規作成する手順はこちらの日記に書いてある。

開発環境

Windows 10

Vivado 2020.1

Zybo(Zynq-7000)

Digilent社のHDMI IPをダウンロードする

今回は、ZYBOの販売元でもあるDigilent社が公開しているオープンソースのIPライブラリに含まれるHDMI IPを使用する。HDMIの規格はHDMIの規格団体に参加している会社や団体しか入手できないので、個人が一から開発するのはなかなか敷居が高い。IPを使うのが一番素直な方法かと思う。

Digilent社のIPライブラリはこちらからダウンロードできる。ダウンロードしたら、Vivadoのプロジェクトのディレクトリの中の適当なディレクトリに置いておく。

ブロックデザインを作成

これまではブロックデザインは使わずRTLコードだけで完結させていたが、今回はブロックデザインでRTLを作成してみる。

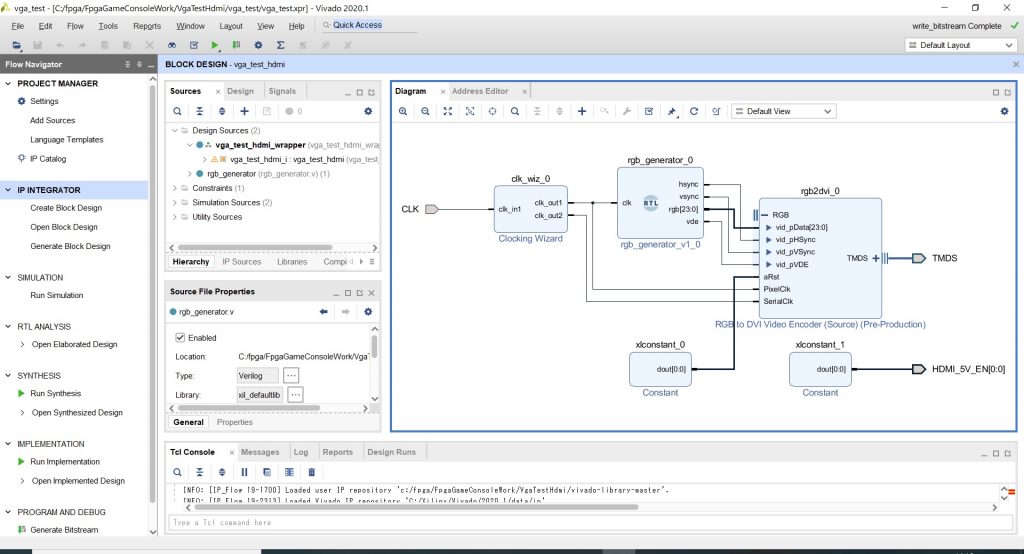

ブロックデザインはIP INTEGRATOR → Create Block Designでブロックデザインを作成する。完成系は以下のようになるが、ポイントを一つずつ書いておく。

DigilentのIPライブラリをインポートする

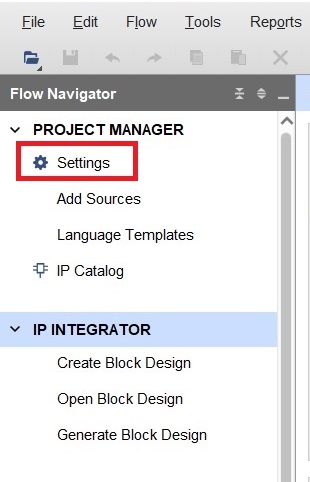

まずは、先ほどダウンロードしたDigilentのIPライブラリをインポートする。PROJECT MANAGERからSettingsを選択。

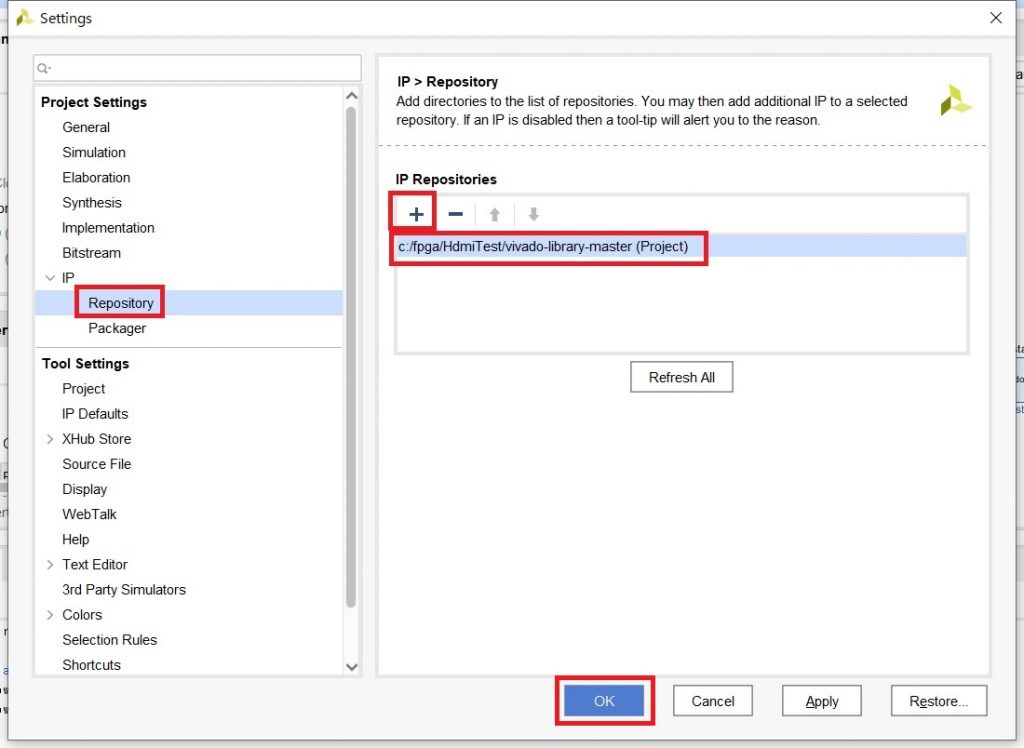

Settingsウィンドウが開いたら、IP → Repositoryを選択して、+ボタンをクリックして、先ほど適当に置いたディレクトリにあるIPライブラリを選択する。追加したらOKを押す。

これでDigilentのIPが使える状態になった。

RTLソースコードをBlock Designでモジュールとしてインポートする

今回私が作成したRTLはgithubに一式置いてある。

https://github.com/WakkyFree/FpgaGameConsole/tree/master/HdmiRtls/RgbGenerator

このソースコードをプロジェクト内の適当なディレクトリに置いて、以下の手順でインポートしてBlock Designに配置して接続する。

Input/Output Portを作成する

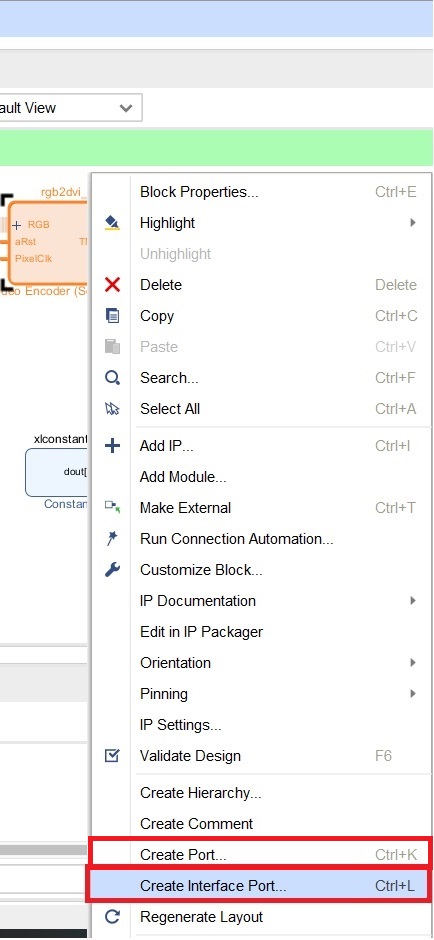

次にInputとOutputのPortを作成する。ブロックデザインのダイアグラム上で右クリックし、「Create Port…」を選択。

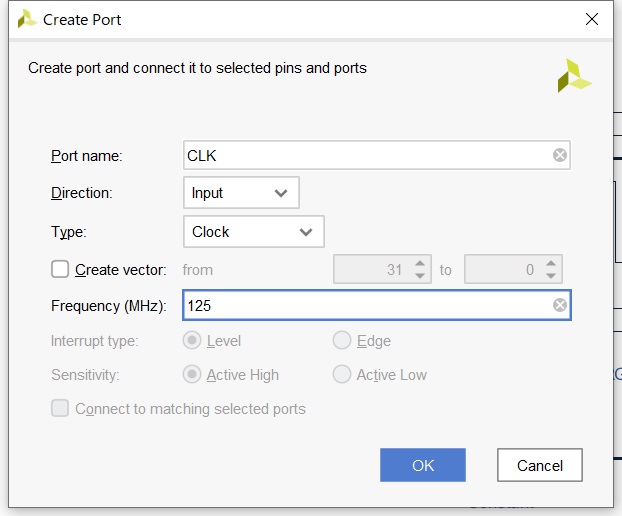

CLKという名前でFPGAに入っているされているクロック用のInputポートを以下のようにつくる。

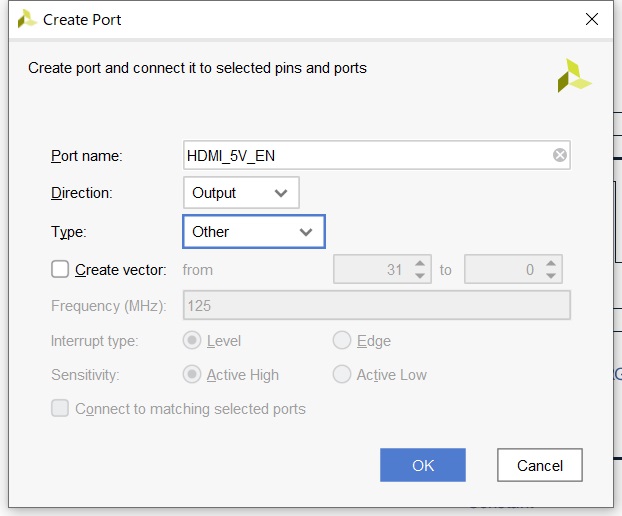

また、HDMI_5V_ENという名前のOutputポートをつくる。これはテレビやモニターなど受信側の機器(Sinkと呼ぶ)と接続したときに映像を送信する機器(と呼ぶ)から供給する+5VをHIGHにするための信号。

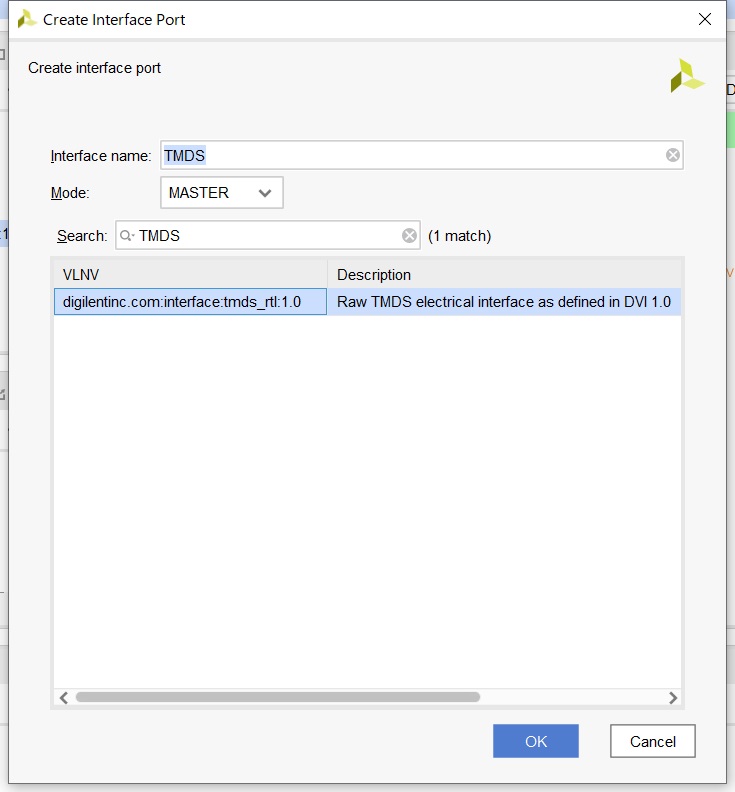

HDMI IPから出力するHDMIのビデオ&クロック信号のPortは、Create Portではなく「Create Interface Port…」で作成する。名前はTMDSとした。Searchで「TMDS」と打つと、以下のように出てくるはずなので、こちらを選択してOK。

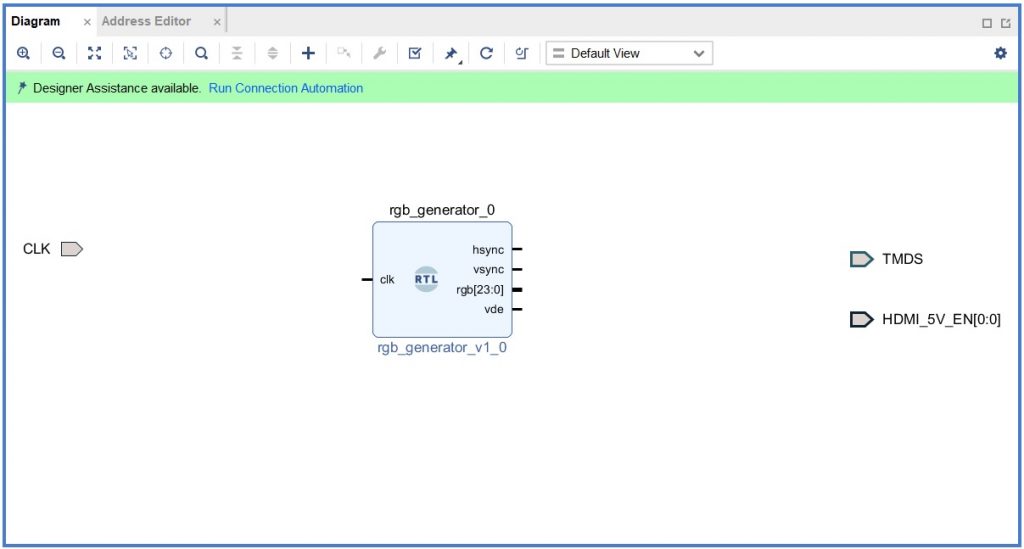

ここまでやると、以下のような状態になっているはず。

次はIPの設置や設定…なのだが、ちょっと長くなったので、続きは次回書きたいと思う。

FPGAでゲーム機をつくろう日記まとめ

この日記は以下でまとめています。