Vivadoのプロジェクトをtclから生成する

前回、Vivadoのプロジェクトをtclファイルに書き出す方法を書いた。今回は逆にtclからVivadoのプロジェクトを生成する方法を書いていく。

環境

Windows 10

Vivado 2020.1

tclファイルからVivadoのプロジェクトを生成

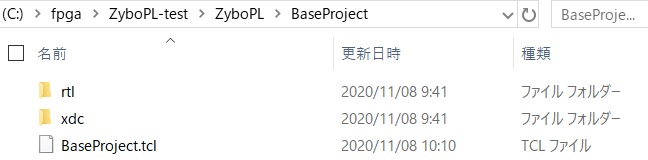

今回は、前回作成したtclからVivadoのプロジェクトを生成してみる。私がgithubで配布しているprojectを落としてきたtclからプロジェクトを生成することを想定して、以下のようにrtlとxdcがあるディレクトリに置いたtclファイルからvivadoプロジェクトを生成する方法を書いていく。

※tclを生成した時のディレクトリ構成と、tclを生成するときのディレクトリ構成が異なっていると、生成したプロジェクトでうまくrtlとxdcファイルがうまく読み込めないので注意。tcl生成後にディレクトリ構成を変更したい場合は、tclに書いてあるディレクトリを書き換える必要がある。

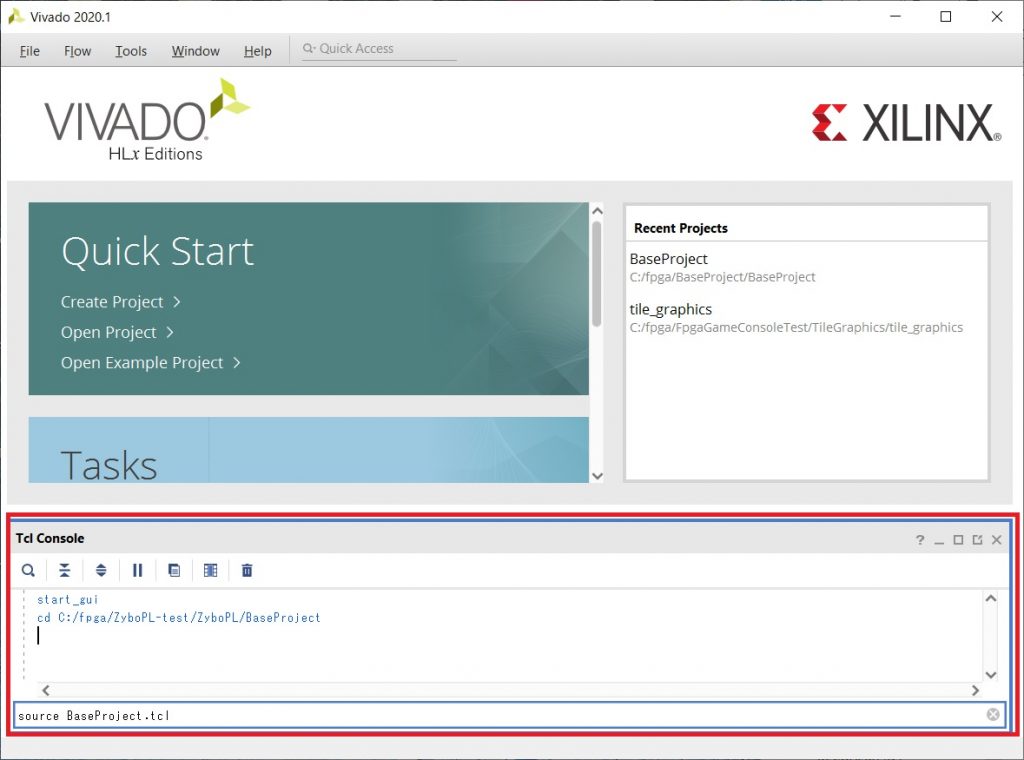

まず、Vivadoを立ち上げる。特にプロジェクトは開かず、単純にVivadoを起動してtclを実行できるようにすればOK。Vivadoを起動すると下の方にtclのコマンドを実行するウィンドウがある。ここでcd コマンドを使ってtclファイルが置いてあるディレクトリに移動し、sourceコマンドでtclファイルを指定して実行する。

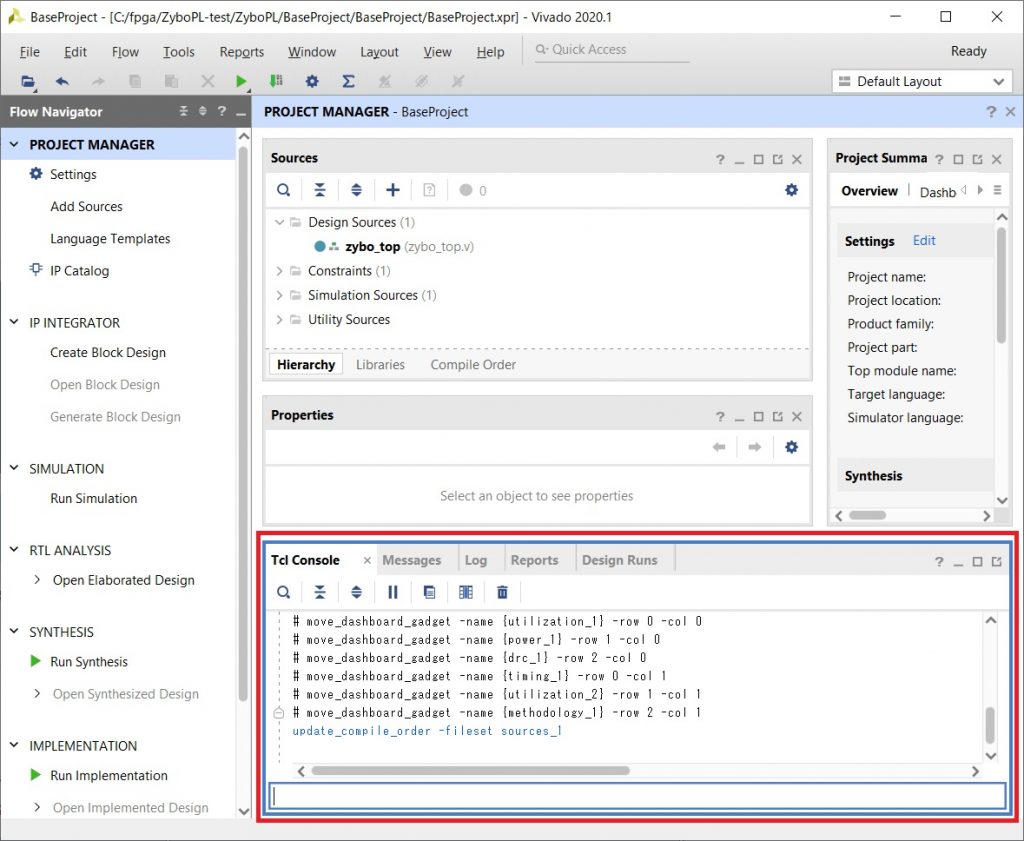

エラーなくプロジェクトの生成が終われば、以下のように表示されてプロジェクトの生成は完了。

あとはRTLや制約ファイルのディレクトリ構成がtclに書いてある参照先の通りになっていれば、問題なくsynthesisとimplementationができるはず。