この日記でやること

Vivado HLSの高位合成を使って、ZYBOのLEDを点滅させてみる日記の5日目。前回はC++のコードからHDLのコードを生成してみたが、HDLに不要なポートが付加されていた。今回は、Directiveを指定して、HDLコードを最適化してみる。

環境

Windows 10

Vivado HLS 2018.3

ZYBO

ソースコードの中にDirectiveを追加する

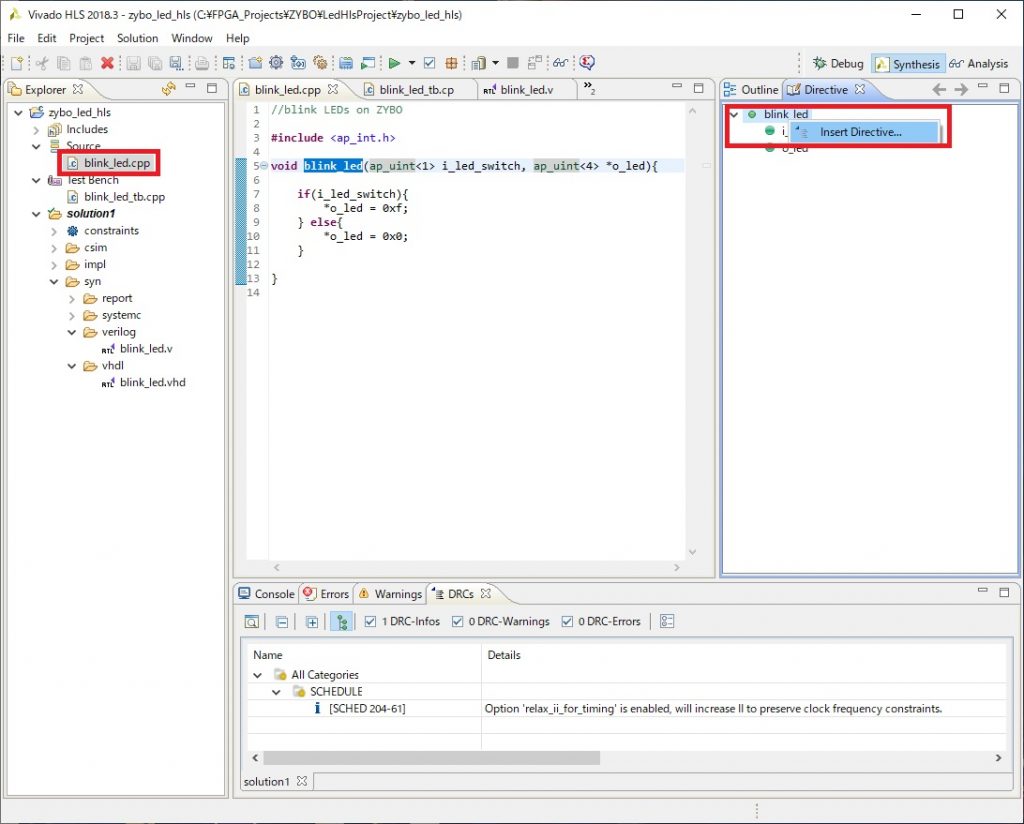

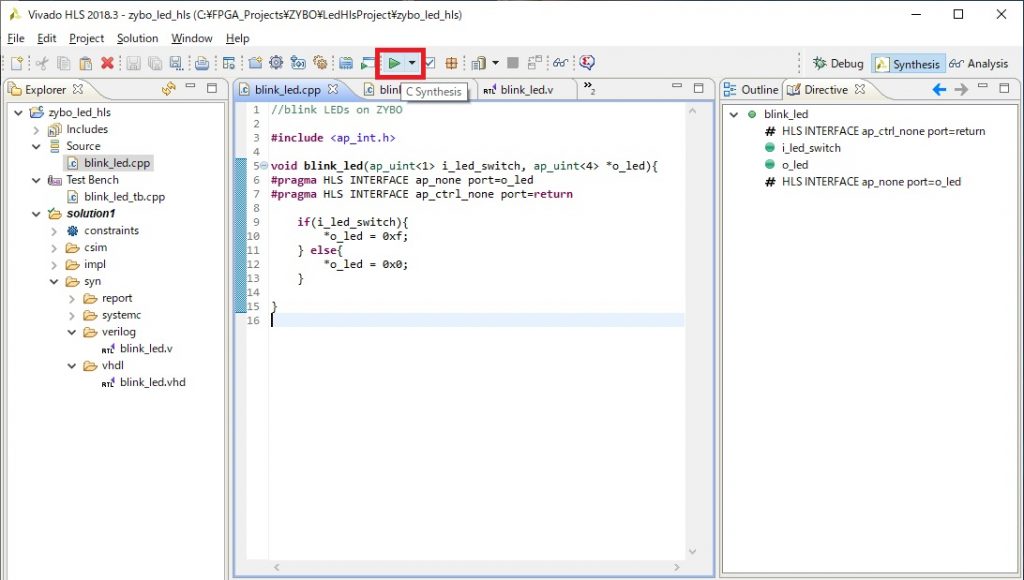

前回生成したHDLの中にap_start、ap_done、ap_idle、ap_readyというポートと、o_led_V_ap_vldという不要な入出力ポートがあるので、Directiveを指定して再合成することでこれらを削除する。まず、Explorerからblink_led.cppを選択して、右側のDirectiveのblink_ledを右クリックし、Insert Directive…を選択する。

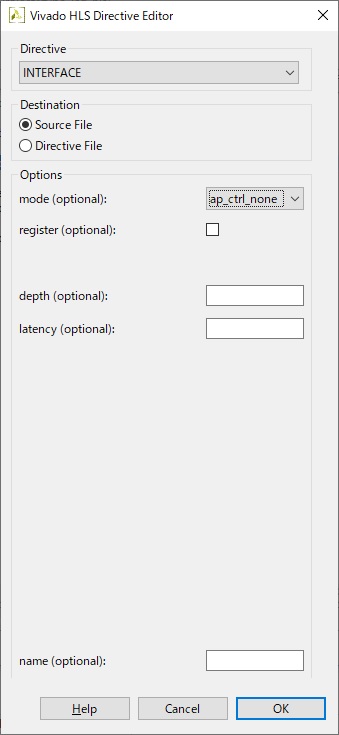

するとDirective Editorが立ち上がるので、以下のように設定してOKをクリックする。

すると、ソースコードの中に

#pragma HLS INTERFACE ap_ctrl_none port=return

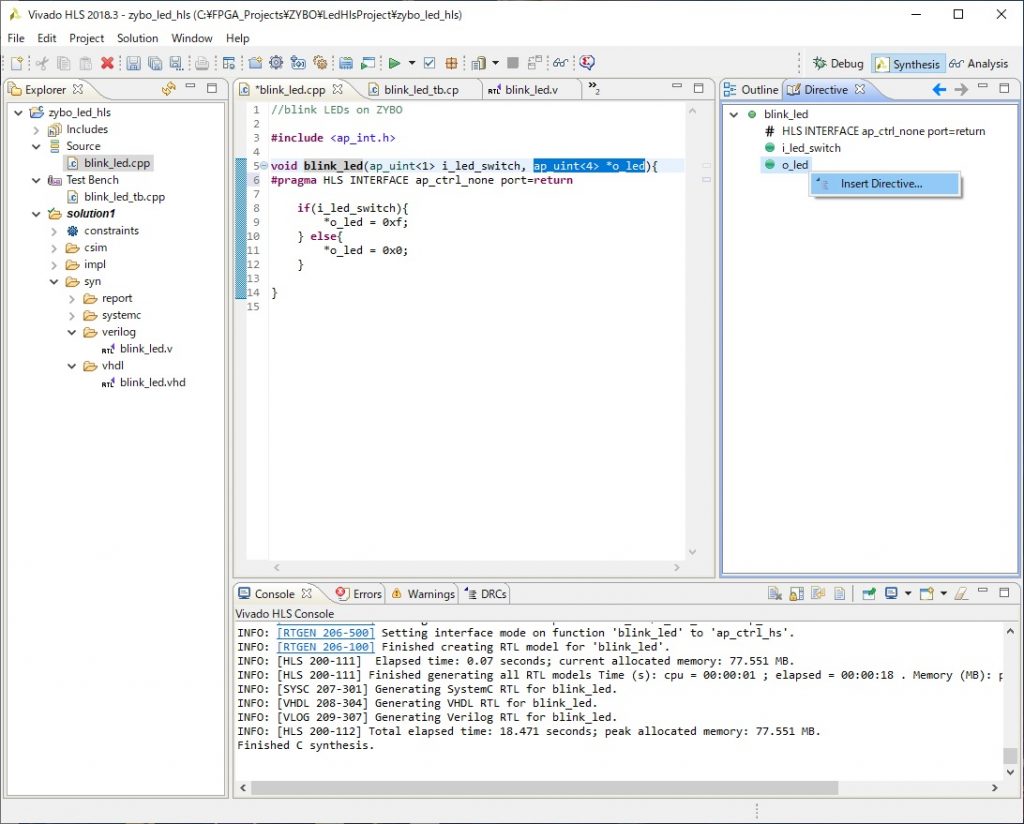

というDirectiveが追加された。この状態で再度合成を行えば、ap_*ポートが無いHDLファイルを生成することができる。さらに、o_led_V_ap_vldを消去するために、同じ要領でo_ledをDirectiveタブで選択して右クリックし、Insert Directive…を選択する。

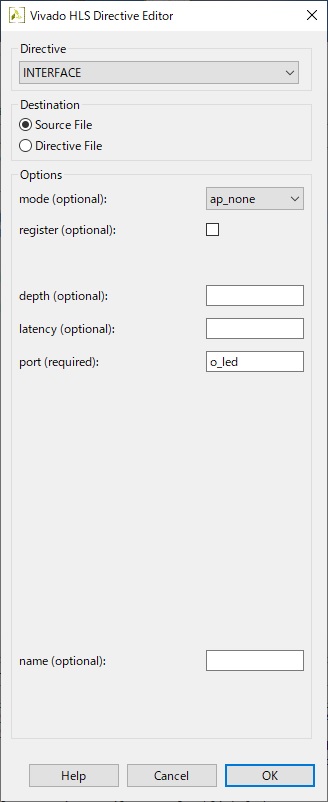

先ほどと同じように以下のように設定してOKをクリックする。

すると、ソースコードの中に

#pragma HLS INTERFACE ap_none port=o_led

というDirectiveが追加された。この状態で合成を行うと、o_led_V_ap_vldが消去される。Directiveがソースコードに追加されたら、blink_led.cppを保存する必要があるので注意。

Directiveが追加された状態で再合成する

Directiveがソースコードに追加された状態で、C Synthesisを再度実行する。

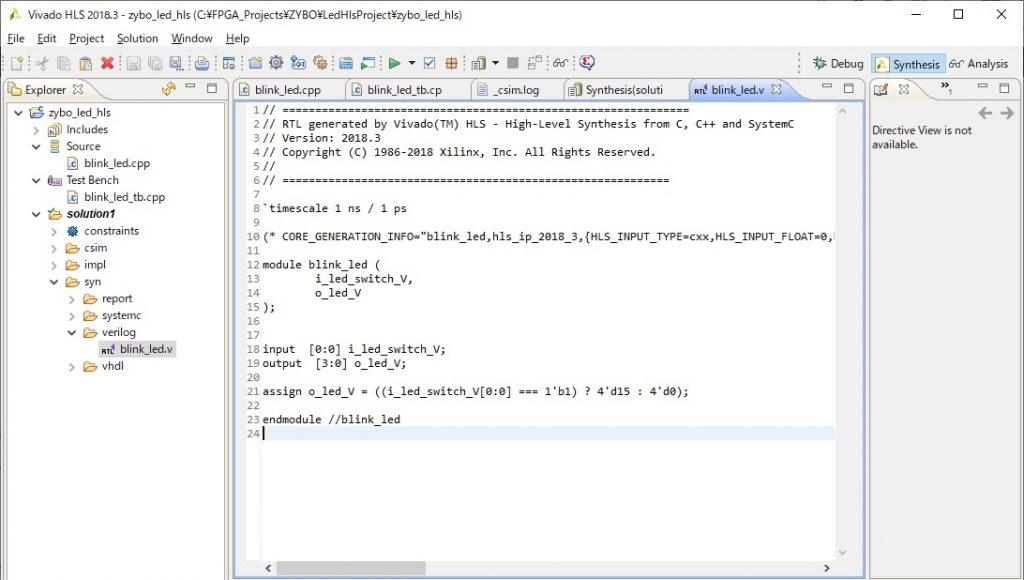

生成が完了したら、verilogのコードを開いてみる。不要なポートが消え、assign文だけのシンプルなHDLになっていることがわかる。このくらい簡単な回路なら高位合成を使ってもありがたみがあまり無いのだが、まぁ今回は高位合成ツールを使う練習なので良しとする。

次回は生成されたverilogのコードを、以前作ったzybo用のRTLに組み込んでLEDを点滅させてみたいと思う。

参考文献

公式のドキュメントが以下にあるので、参照しながら進めていきます。

UG871:Vivado Design Suite Tutorial – Hi-Level Synthesis

UG902:Vivado Design Suite User Guide – Hi-Level Synthesis

以下の資料も参考にさせて頂きました。

https://www.slideshare.net/marsee101/vivado-hls1

ZYBOで遊ぼう日記まとめ

ZYBO関係の記事は、大まかな内容ごとに以下にまとめています。

https://wakky.tech/zybo/